1.光刻(Lithography)

三个主要过程:Coating

1.1 Light Intensity

Mercury Arc Lamp: V Light Wavelength大概在300-400nm之间时,也就是g-line、h-line、i-line光刻胶,用的是深汞灯(Hg lamp)进行光刻,光刻强度低(low intensity),因此所需曝光时间长。

Excimer laser Source(准分子激光源): 而当UV Light Wavelength下降到300以下时,就是KrF光刻胶,用的是Deep UV(DUV),也就是深紫外灯,其拥有更高的光刻强度(high intensity),则所需曝光时间就很短.

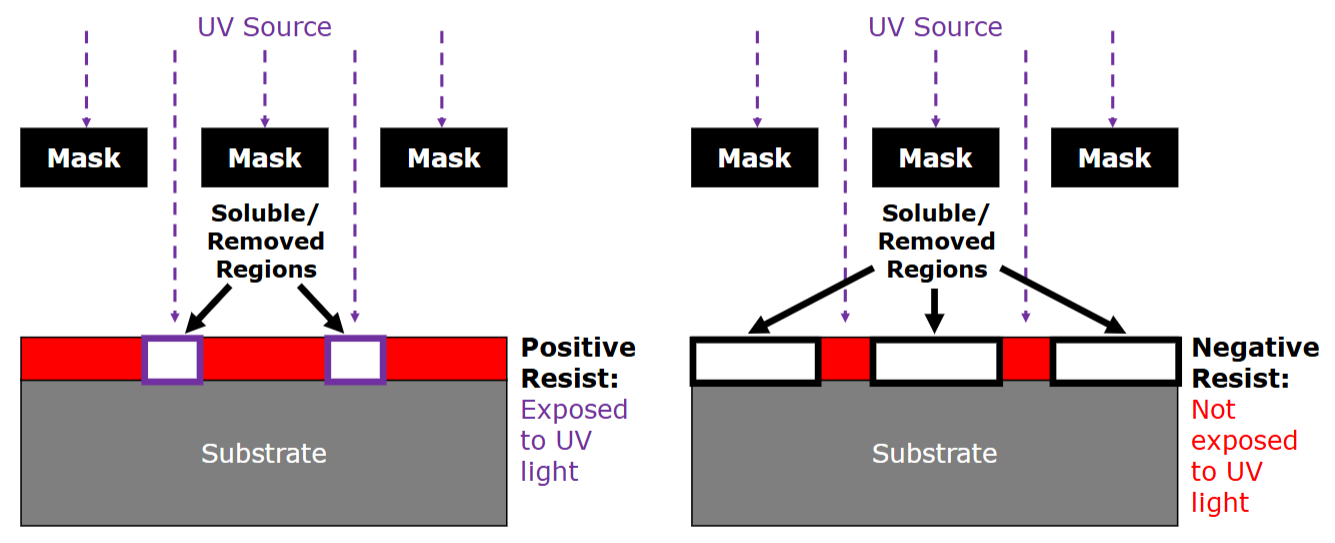

1.2 Resists

如上图所示,左边是正性光刻胶,被UV光照的地方溶解,而有掩膜(Mask)遮盖的地方,也就是没有光照的光刻胶不溶解;而右边则是负性光刻胶,其工作机理与正光刻胶相反,被光照的光刻胶不溶解,而被掩膜遮盖的位置则溶解。

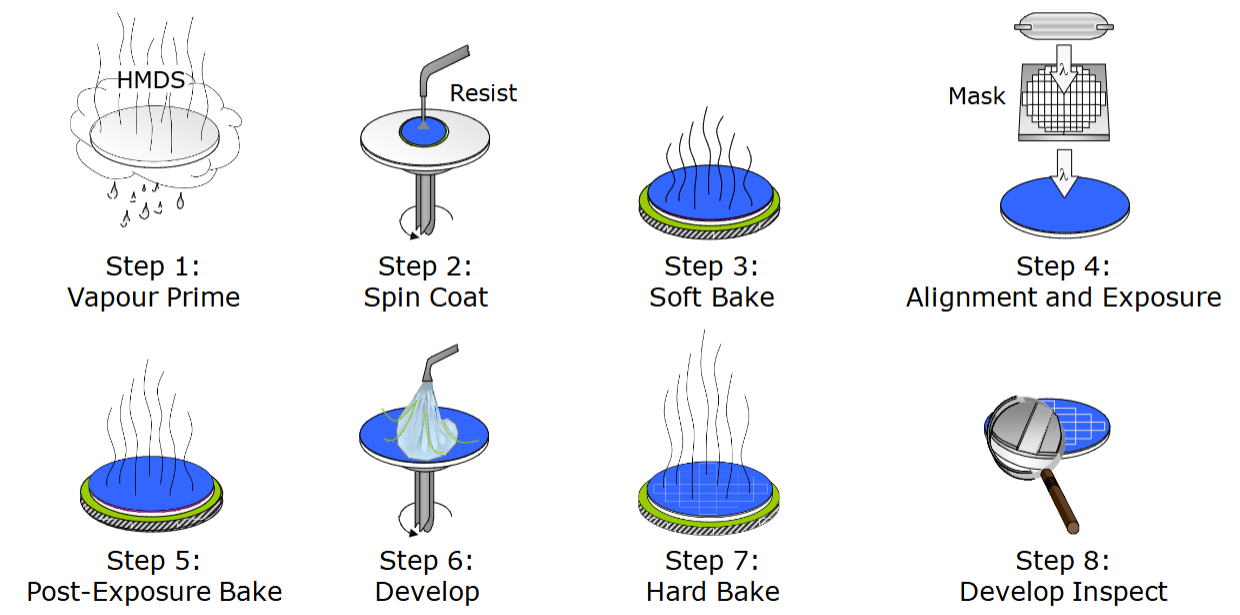

1.3 Eight Steps of Lithography

step 1: Vapour Prime

① Wafer dehydration bake; ② HMDS adhesion clean and dry.

step 2: Spin Coat

① Make PR to expected Thickness;

另外,Resist layer thickness depends on the viscosity of resist and is inversely proportional to the square root of the spin speed,

Thinner Resist:

step 3: Soft Bake

① Partial evaporation of resist solvents; ② Improves resist-to-wafer adhesion; ③ Improves etch resistance

短时间的Pre-bake可以防止由于残留在PR中的的solvent过多而导致的UV light reaching the PAC;

Over-bake则会增加sensitivity to UV light,甚至可能破坏PAC和减少solubility of the PR。

step 4: Alignment and Exposure

① Transfer pattern to wafer; ② Active PAC

step 5: Post-Exposure Bake

① Evaporate all solvnent

还能减少驻波(standing wave)效应的影响

step 6: Developing

① Remove the soluble portion with a solvent; ② Patterning

step 7: Hard Bake

① Evaporate solvnent from step6 adhesion; ② Etch resistance

step 8: Develop Inspect

① Check the quality of process to ensure the pattern is transfered

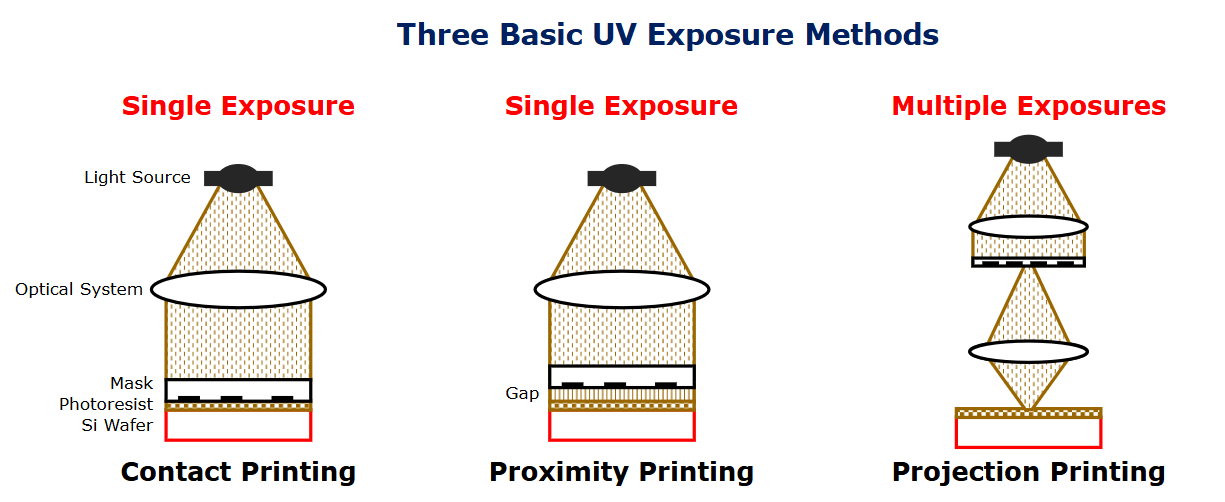

1.4 Printing

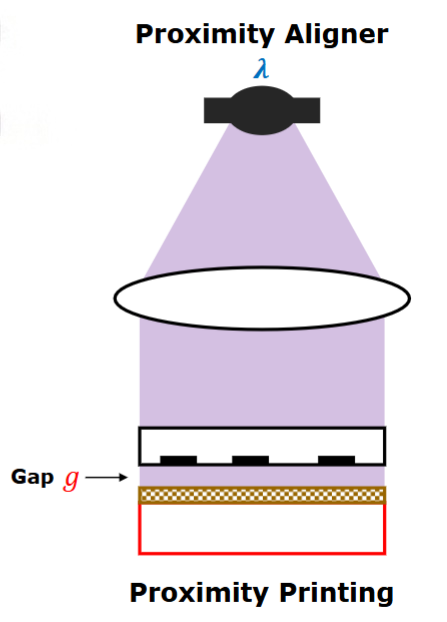

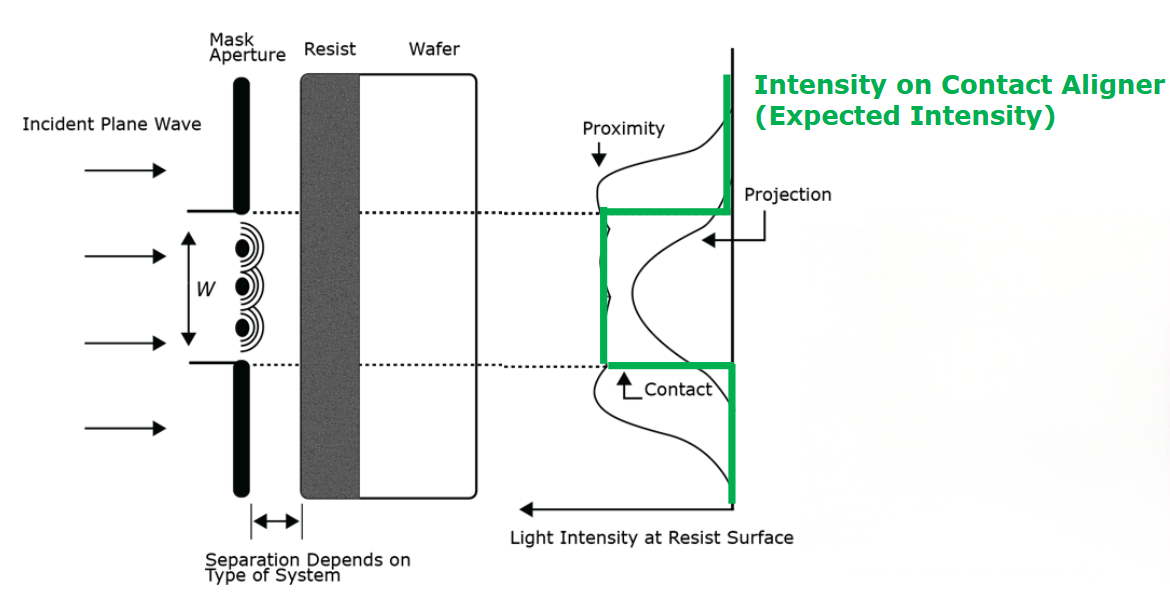

注意:在Contact Printing和Proximity Printing中,掩膜被称作mask,但是在Projection Printing中,则被称为reticle,但实际上两者是一样的。

另外,在Contact Printing中,mask和photoresist是直接接触的;而在Proximity Printing中,mask和wafer并没有直接接触,这一改动可以prevent dust particles。

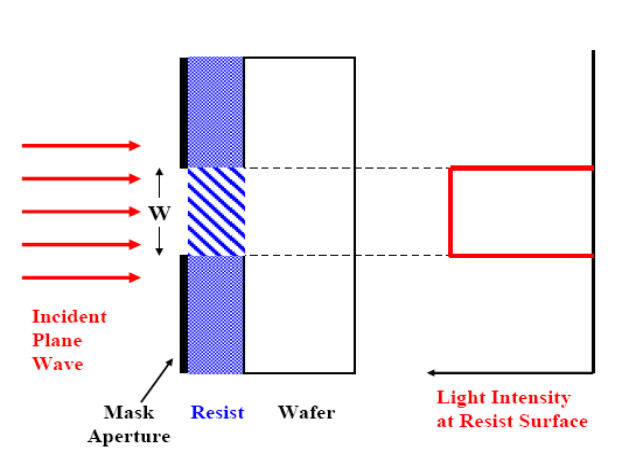

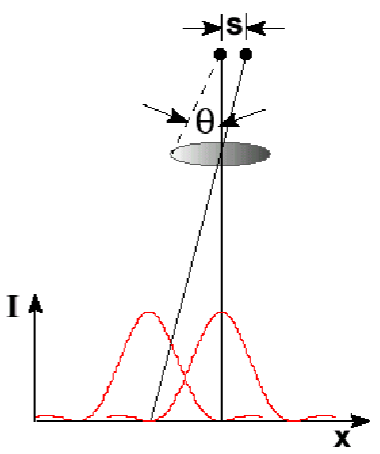

1.5 Minimum Linewidth / Resolution

Resolution for the proximity printer:

and smaller

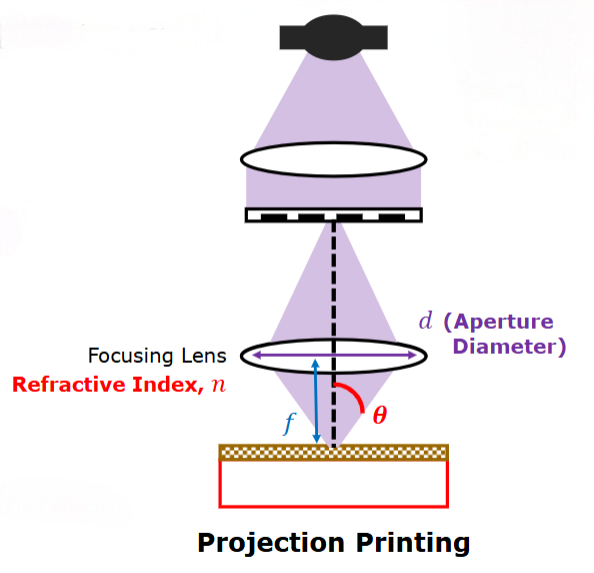

1.6 Numerical Aperture

NA is a measure of the ability to collect light

Where

So n is for air or water not for LENS.

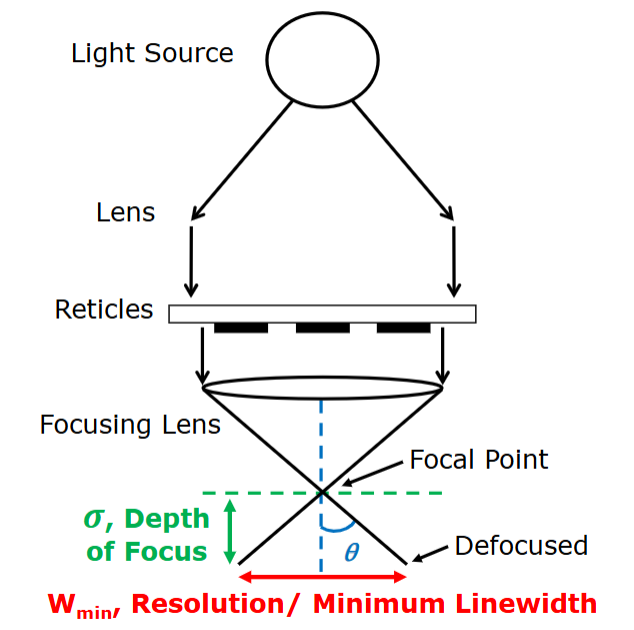

1.7 Depth of Focus

Depth of focus:

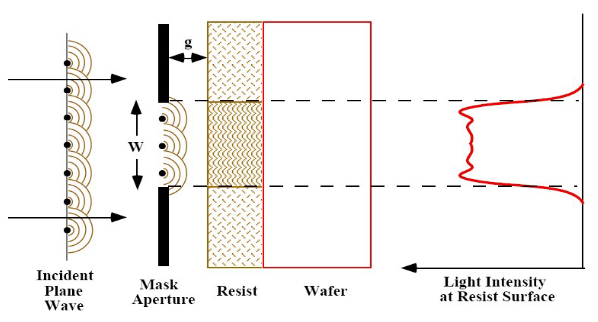

1.8 光强度图

Contact 是正好的矩形;Proximity 是有纹波的阶梯;Projection 是小山丘。

第一张是Contact Printeing,第二张是Proximity Printing,最下面这张图是Projection Printing

上面的光强度图要求要会画,三种光刻模式都要会。

1.9 Modulation transfer function (MTF)

We hope projection printer shows no diffraction, like contact printer light and dark edge is very sharp.

MTF is for optical system (Lens) and bigger is better.

2 光刻胶技术(resist technology)

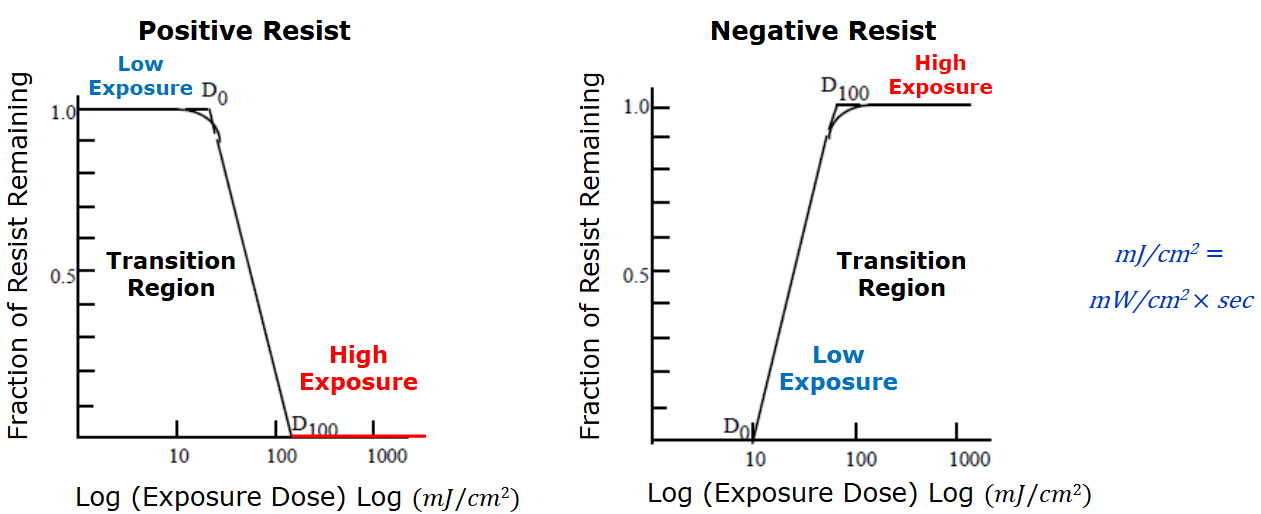

2.1 Contrast curve

A good resist, Dose critical is 50,

You shine 51 dose, all resist is soluble;

You shine 49 dose, nothing happened.

一个重要的参数:

Sensitivity:

Chemical contrast

2.2 Critical Modulation transfer function (CMTF)

从上面的

2.3 Components of Resist

① Resin(树脂)

Give resist mechanical and chemical properties.

② Sensitiser(光敏)

Photo active compound (PAC/ PAG) .

③ Solvent(溶剂)

Keeps resist in liquid state;

Allows spin coating of the resist.

④ Additives(添加剂)

Improve Etch resistivity and implant blocking capability.

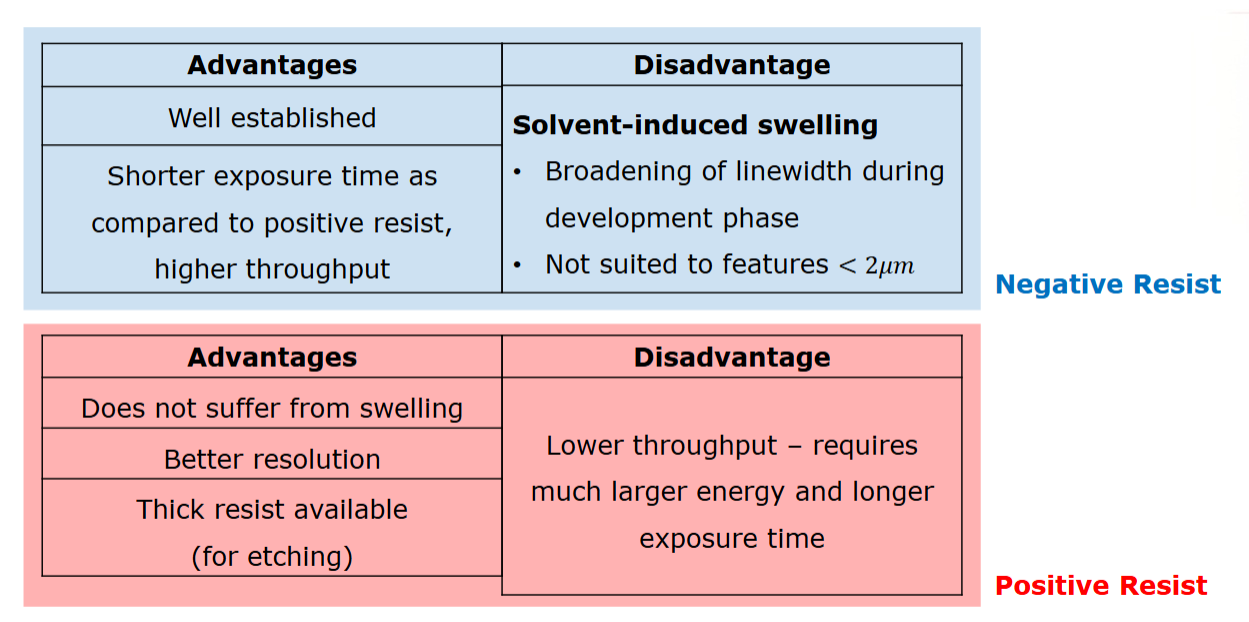

2.4 Advantages and Disadvantages of Resists

注意:正光刻胶是在光照中被溶解,而负光刻胶是在光照中被固化。

现在工业中更喜欢使用正光刻胶,因为有更好的Resolution。

2.5 Chemically Amplified DUV Resist(化学放大深紫外光刻胶)

关键是CA Chemical Amplify:

DUV resists makes PAG (Photo Acid Generator) to generate acid, PEB diffusion acid

2.6 Standing wave effect

解释:Input light reflected and diffusion with reflected light, standing wave formed Zigzag or swing curve

如何减少驻波效应:

① Dye PR more absorption

② PEB flat the zigzag(PEB also helps by smoothing out the zigzag due to resist thermal reflow)

③ ARC anti-reflective

3 先进光刻(Advanced Lithography)

有以下几种:

- Optical enhancement techniques

- Immersion lithography

- X-ray lithography

- EUV Lithography

- E-beam and SCALPEL lithography

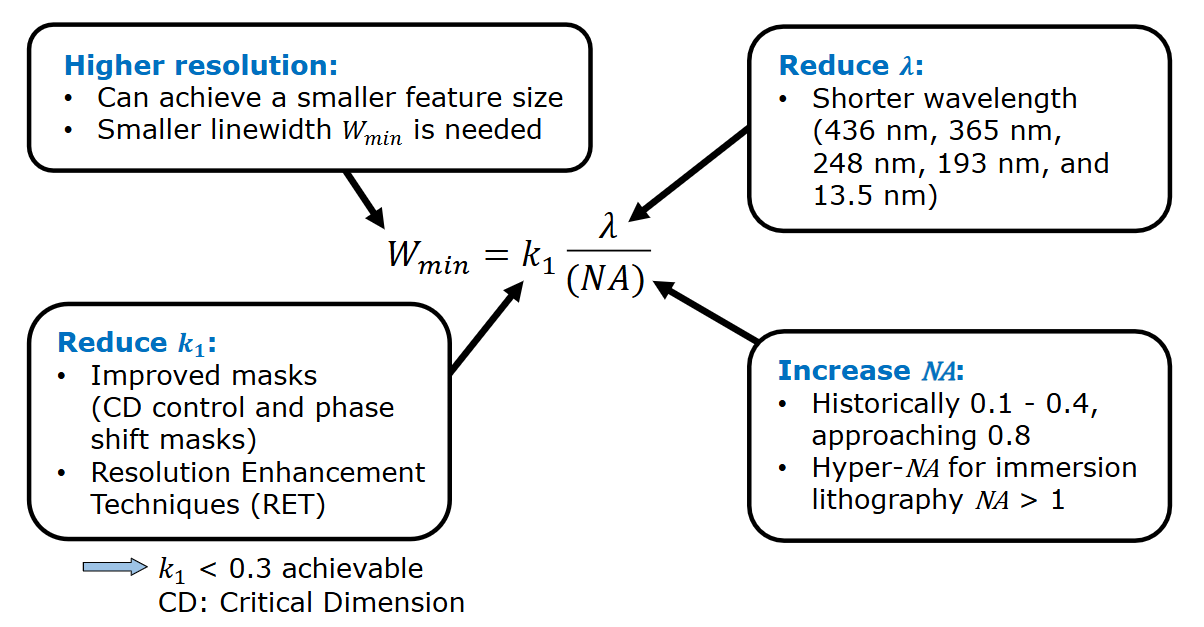

而要提高分辨率,我们先来看看有几种方式:

3.1 光学增效技术(Optical enhancement techniques)

以下所有的内容的考试要求:会画图加上面那段话背下来会解释即可。

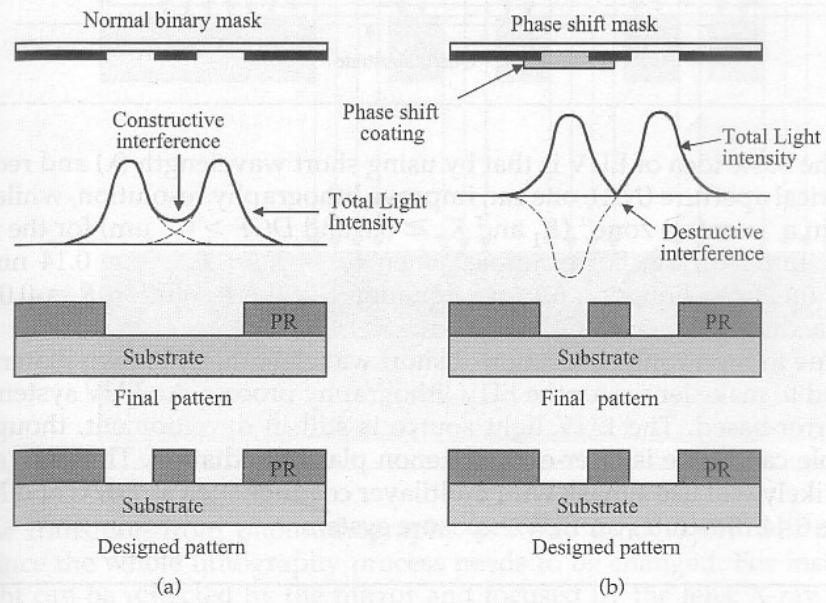

3.1.1 相移掩膜(Phase Shift Mask)

With PSM, the reticle is modified with an additional transparent layer so that alternating clear regions cause the light to be phase-shifted 180°.

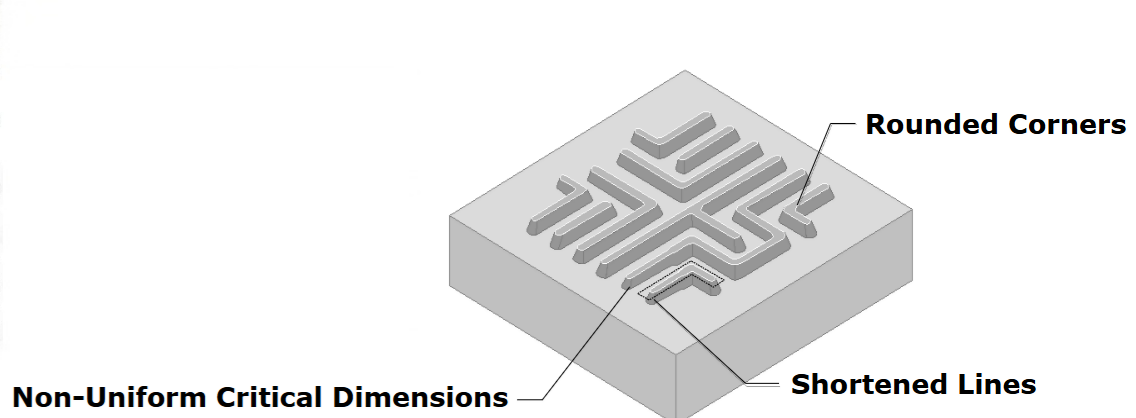

3.1.2 光学邻近校正(Optical Proximity Correction)

The approach involves adding extra features to the mask, usually at corners where features are sharp, to compensate for the high-frequency information lost due to diffraction effects.

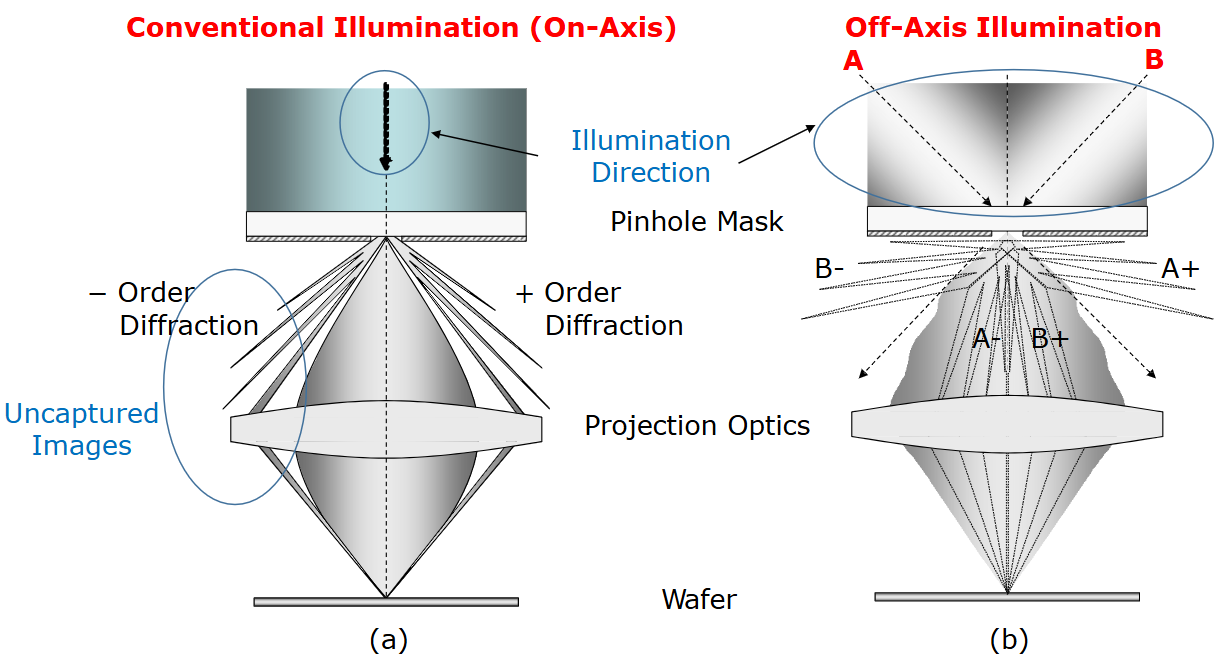

3.1.3 离轴照明(Off-Axis Illumination)

If the incident light source is illuminated at an angle with respect to the lens system(off-axis), higher order diffracted rays can be collected using the lens of the same size.

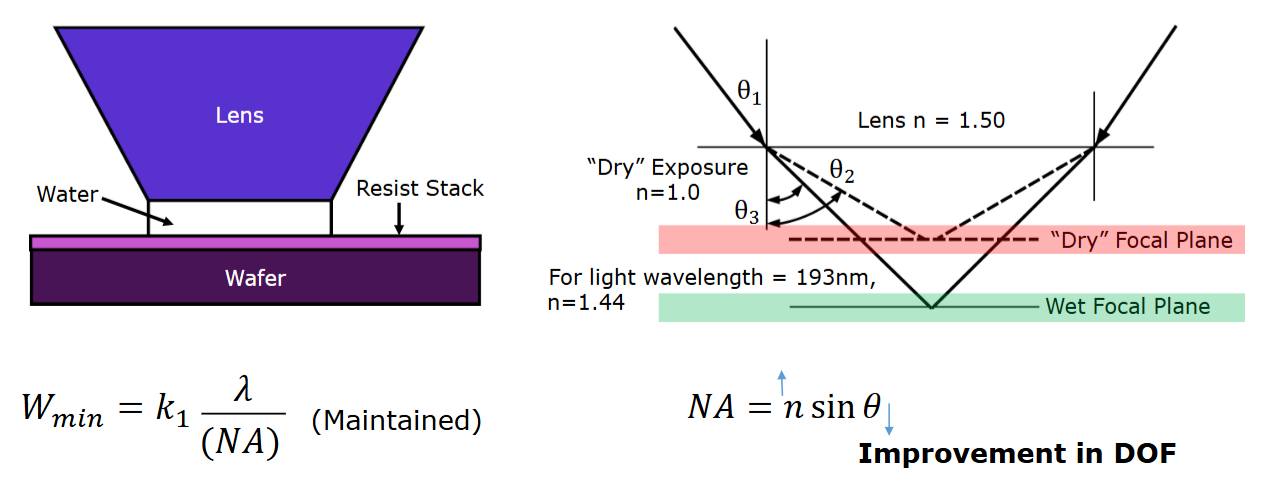

3.2 浸润式光刻(Immersion Lithography)

有两种方法:

- Approach 1:

- Same lens column design

- Maintain resolution

- Improve Depth of Focus (DOF)

- Approach 2:

- Modified lens column: Hyper-NA (

- Improve resolution

- Lower DOF(牺牲 了DOF)

- Modified lens column: Hyper-NA (

这里着重讲一下方法一,这一方法是通过保持

注意:

方法2:Modified NA

3.3 X-ray lithography

这块内容只需要知道优缺点即可。

优点:

- High resolution

- Reduced diffraction effect

缺点:

-

Expensive X-ray source

-

Absorption problem (mask)

-

Shadowing errors

-

Non-monochromatic X-ray source

-

Low throughput

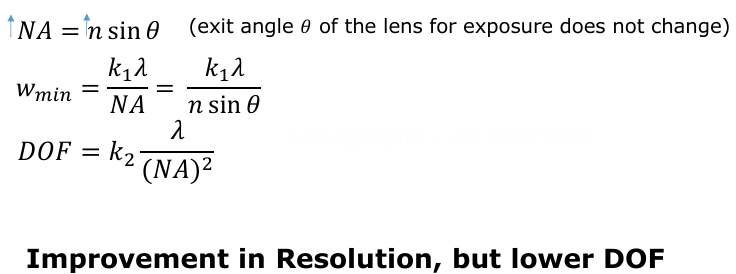

3.4 EUV Lithography

给出下面这张图能认出来是EUV光刻即可,当然最好还是记一下名称啥的:

工作原理:

- Light Source: Utilizes 13.5 nm extreme ultraviolet (EUV) light, whose ultra-short wavelength enables nanoscale ultra-high resolution.

- Optical System: Employs an all-reflective Mo/Si multilayer film optical system, adapting to EUV’s strong absorption by conventional materials to achieve pattern demagnification.

- Exposure: Projects the circuit pattern from the reflective mask onto the wafer’s photoresist to form a latent image.

- Pattern Transfer: Completes high-precision pattern transfer via development, supporting 7 nm and below advanced chip manufacturing processes.

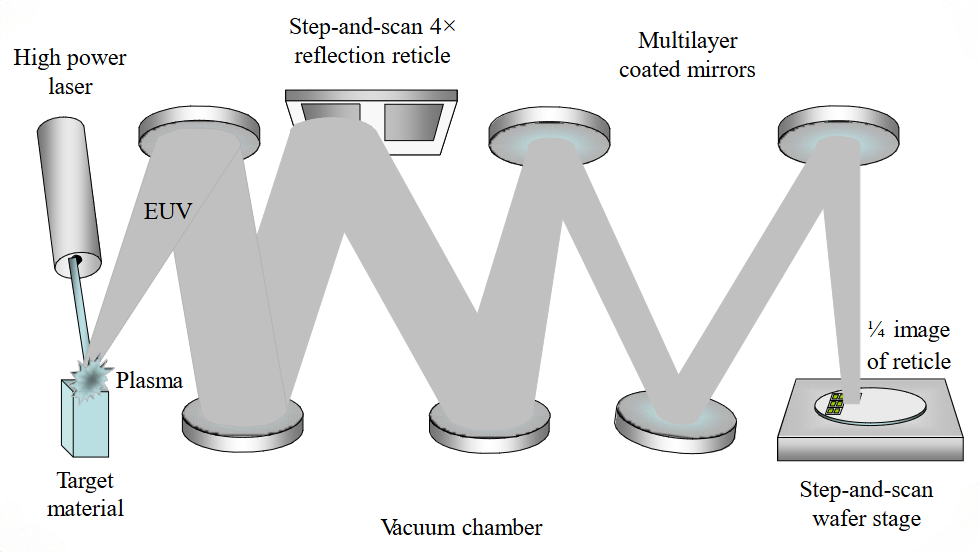

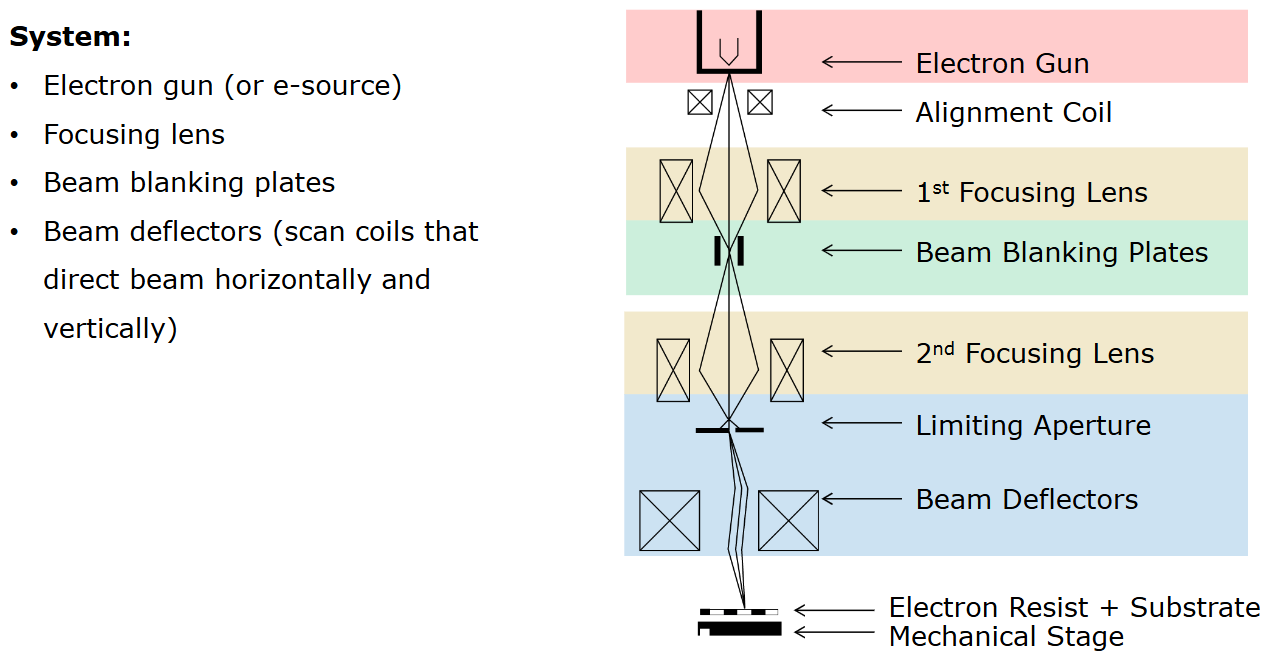

3.5 E-beam lithography

最好会画图,并且知道各部分器件名称:

因为光学光刻的分辨率受衍射极限(瑞利判据)的限制,而电子的德布罗意波长远小于光学波长(193nm/EUV 13.5nm),因此理论上完全不受衍射限制,这也是电子束光刻超高分辨率的根本原因。电子的德布罗意波长公式如下:

在上面式子中,

Example:

Discuss the implication to the maximum allowable proximity gap of the exposure systemmentioned in previous question (A lithography exposure system deploys an Hg arc lamp with three available wavelengths – 436nm (g-line), 405nm (h-line) and 365nm (i-line) respectively. ), if:

a. The optical source is changed to X-ray as opposed to Hg arc lamp used in the earliercase.

b. Phase shift masks are used in the exposure.

Answer:

a. If the optical source is changed to X-ray as opposed to Hg arc lamp used in the earlier case,

λ is smaller, larger g (max allowable proximity)

b. If the phase shift masks are used in the exposure, k is smaller, larger g (max allowable proximity)

4 干法刻蚀(Dry Etching)

最重要的一句话:Dry etch uses gas phase etchants in plasma.

为什么要选择干法刻蚀,有下面三个原因:

-

Achieve desirable profile (slope or vertical)

-

Minimal undercut

-

Uniformity and reproducibility

4.1 干法刻蚀中的各向异性(Anisotropy)

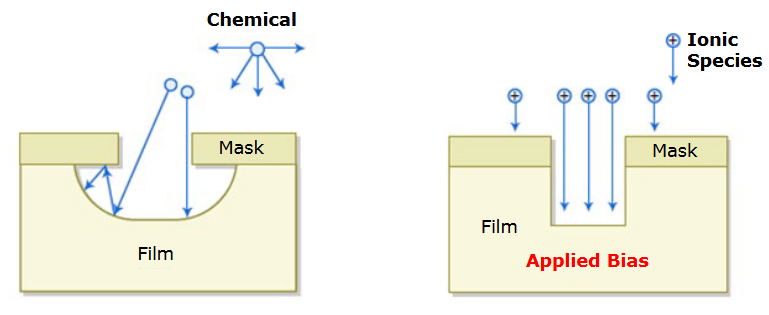

上图是刻蚀工艺中各向同性(Isotropic)和各向异性(Anisotropic)刻蚀的对比。

左边表现出的是各向同性:其是由于化学粒子(Chemical)做无规则、各方向的随机运动,因此没有定向性,会从上下左右各个方向攻击薄膜,形成的沟槽宽度就会大于掩膜开口。

右图则是各向异性,它的形成是由于离子(Ionic Species)在外加偏压(Applied Bias)的电场作用下,做垂直向下的定向(directional)运动,只攻击沟槽底部的薄膜,几乎不攻击侧壁,因此其沟槽宽度和掩膜开口几乎一致。

Degree of Anisotropy:

其中:

4.2 等离子体(Plasma)的产生与过程

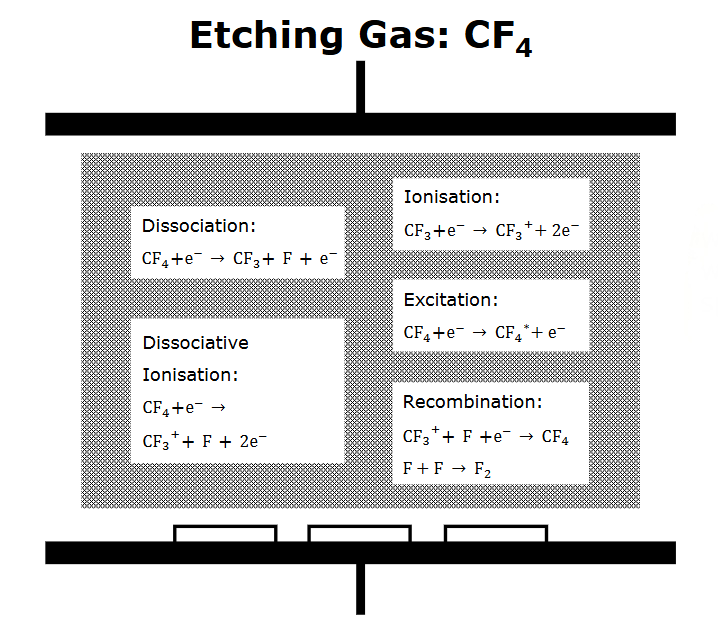

这节最重要的就是下图:

这张图只要记住等离子体是如何产生的即可,方程式可以不用记住,大概就是下面这四个过程:

- Dissociation

- Ionisation

- Excitation

- Recombination

4.3 等离子体与基底的相互作用

主要有两种形式:

一种是纯物理刻蚀,其作用机制是表面被高能离子轰击,离子在表面的动能损失主导整个相互作用过程。

另一种就是物理-化学复合刻蚀,它的作用机制相比起纯物理刻蚀,其轰击离子引发的化学腐蚀作用也参与刻蚀过程,是物理轰击与化学反应的协同作用。

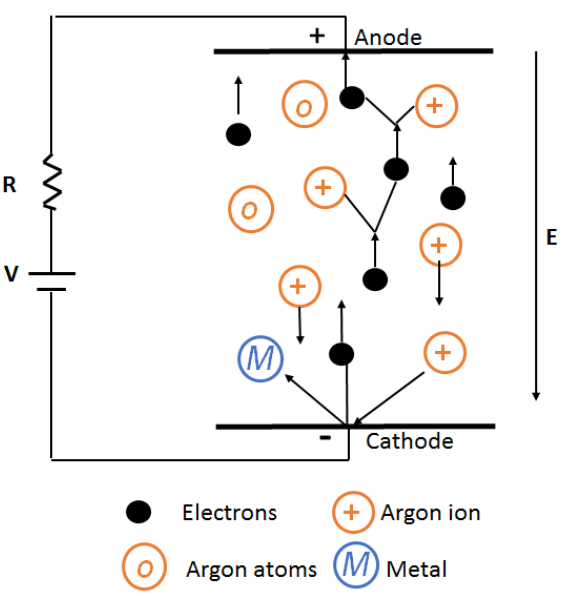

4.3.1 溅射刻蚀(Sputtering Etching)

用直流 / 射频(DC/RF)电源激发氩气(

图不要求掌握,但上面的过程要能自己用英文表述出来,关键词已经给出。

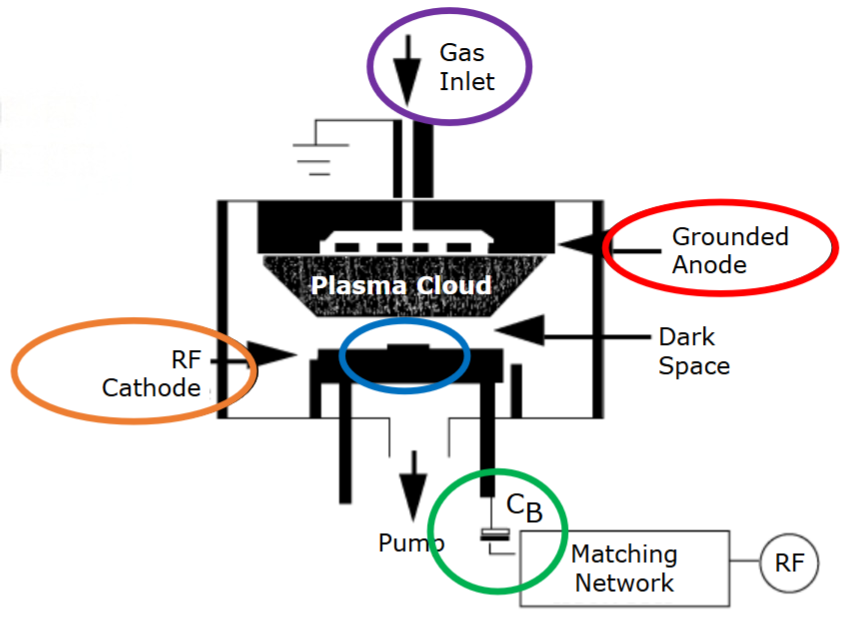

4.3.2 反应离子刻蚀(Reactive Ion Etching)

RIE复合了物理刻蚀和化学刻蚀,用

其中物理刻蚀同样也是离子轰击,这里不再作赘述。主要来阐述化学刻蚀部分,其是反应性刻蚀剂与目标材料反应,生成挥发性产物。

这种复合机制的好处是不仅保留了高各向异性,还同时提高了选择性,也大幅提升刻蚀速率。

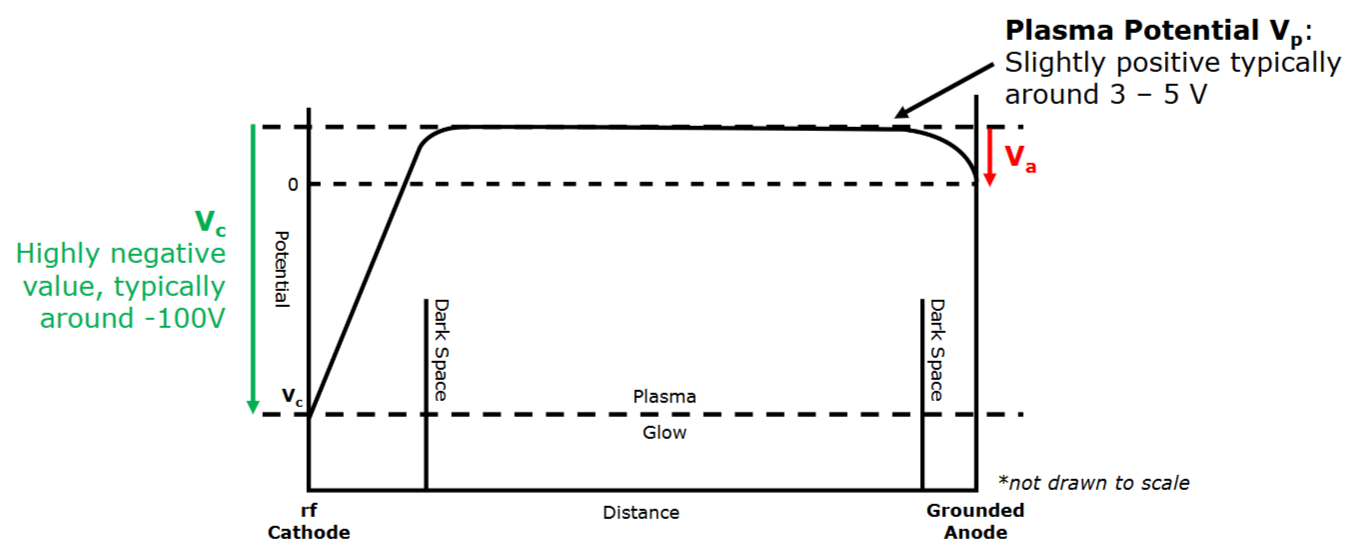

这一节最重要的,也是必考的考点就是下面的组成图和它的工作机理,一定要会画图,并且对其工作机理要能用一段话描述出来:

RIE系统的工作步骤(必考):RF power energizes electrons, which accumulate negative charge on the RF-driven bottom electrode, creating a steady negative self-bias. A plasma sheath (dark space) with high electric field forms around the cathode, accelerating ions vertically to bombard the substrate for RIE etching.

中文对照版:射频源为电子供电,电子在射频驱动的底部电极上积累负电荷,产生稳定的负自偏压。阴极周围形成具有高电场的等离子体鞘层(暗区),垂直加速离子轰击基板进行RIE蚀刻。

同时,这一小节还需要记住一个公式:

其中

该公式表明了,当

然后上面这张图最好也要会画,它很好地表现出了为什么晶圆放在阴极上能获得高刻蚀能量。

其实总结来说,RIE的完整物理化学过程就是下面四个步骤:

- Transportation: The etchant(positive ions) accelerates to the substrate surface.

- Adsorption: The etchant chemisorbs onto the surface of the substrate.

- Reaction with the substrate and the formation of the volatile by- product(gaseous form).

- Desorption of the volatile by-product away from the substrate。

刻蚀的总速率由最慢的那一步决定,跟木桶效应有点像。输运限制(Transportation-limited)是刻蚀剂的输运速率低于刻蚀剂与衬底之间的化学反应,也就是步骤1和步骤4的速率决定了干法刻蚀中的整体刻蚀速率。反应限制(Reaction-limited)是刻蚀剂和衬底之间的化学反应速度远慢于刻蚀剂的输运速度,也就是步骤2和步骤3的速率决定了干法刻蚀中的整体刻蚀速率。

接下来,我们需要记住在Wafer Fabrication中一些用来刻蚀的气体:

For etching of Si-based films, fluorocarbon(

For etching of organic films, oxygen-based chemistry is used;

For etching of metal lines, chlorine-based or fluorine-based chemistry is used.

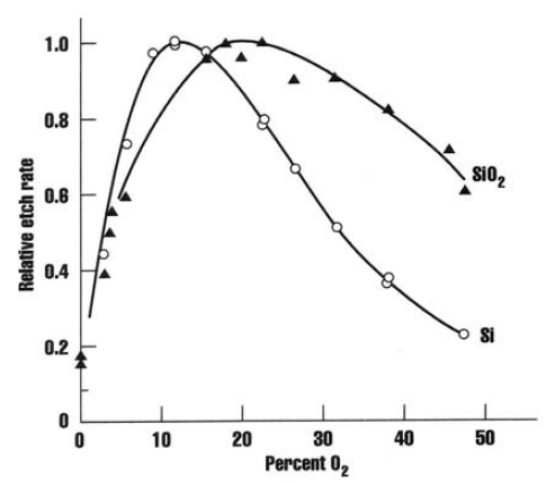

另外,我们还需要考虑一个问题:How does the

原子

-

硅刻蚀:

-

氧化硅刻蚀:

由此很显然,要想提高刻蚀速率,就需要加快活性

该反应会消耗

从而大幅提高等离子体中活性

观察上图,可以发现

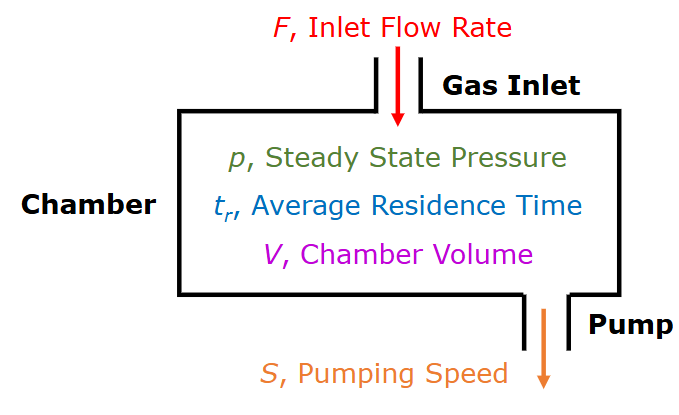

4.4 控制等离子体蚀刻速率的因素

- Steady state pressure

- Average residence time

- Throughput/gas load

在这个图中需要明确三个量:

- 稳态压力

- 平均停留时间

由此,平均停留时间可以被整理为:

当抽速

- 通量/气体负载

4.5 刻蚀的一些问题

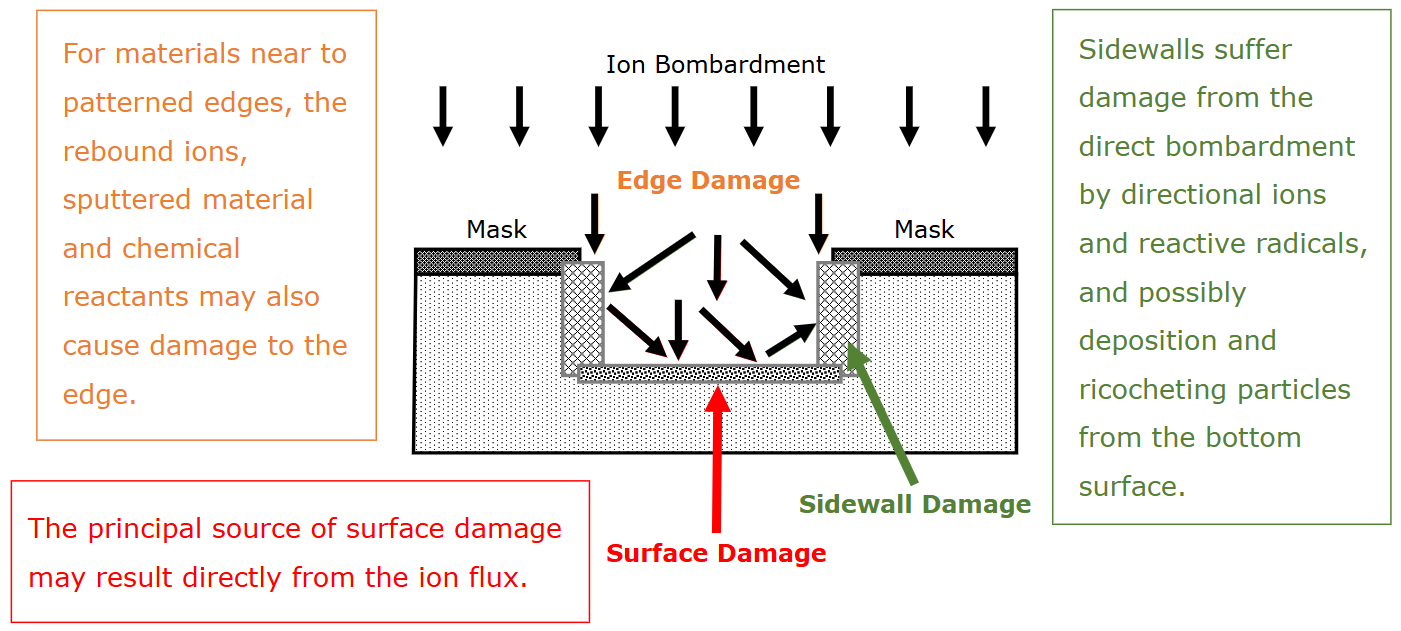

4.5.1 等离子体损伤(Plasma Damage)

在等离子体刻蚀中,高能离子轰击晶圆,会直接破坏材料结构,导致器件的电学和光学性能大幅劣化。而损伤的严重程度,取决于以下两个因素:一个是电场强度,也就是说电压越高,离子能量越高,损伤就越严重;第二个是离子质量,离子的质量越大,轰击动量就越大,损伤越剧烈。

而刻蚀后的晶圆可能出现三种不同位置的损伤,如下图:

等离子体损伤对器件有三大危害:

- Reduce the carriers mobility of semiconductors

- Deactivate dopants

- Increase the resistivity

修复损伤的方法就是退火(Annealing):用快速热处理器(RTP)或高温炉,在

4.5.2 表面污染(Surface Contamination)

这是另一个刻蚀致命问题,核心是微掩模效应。

指纹、灰尘、工艺残留(光刻胶、刻蚀副产物)等污染物,会在半导体表面留下非挥发性副产物(固体 / 液体残留),附着在晶圆表面。这些污染物会沉积在表面,在刻蚀时充当微掩膜(micro masks)。微掩膜会抑制后续刻蚀,导致刻蚀不完全,同时让刻蚀后的表面变得极其粗糙。

4.5.2.1 宏观负载效应(Macroscopic Loading Effects)

待刻蚀的总面积越大,刻蚀剂被消耗得越快,剩余刻蚀剂浓度越低,刻蚀速率就越慢,这就是宏观负载效应。

负载效应可以用一个公式来描述:

其中,

Example:

A plasma etch progress is found to produce an etch rate of 30 nm/min when etching a single wafer of 200 mm in diameter. When the same etching recipe is repeated on another wafer with 200 mm diameter with twice the etch pattern area, the etch rate falls to 20 nm/min.

Answer:

Estimate the etch rate is if the etch pattern area is tripled on another 200 mm wafer.

Substituting the data gives:

Solve the two equations and you will get:

Therefore,

4.5.2.1 微观负载效应(Micro-loading Effects)

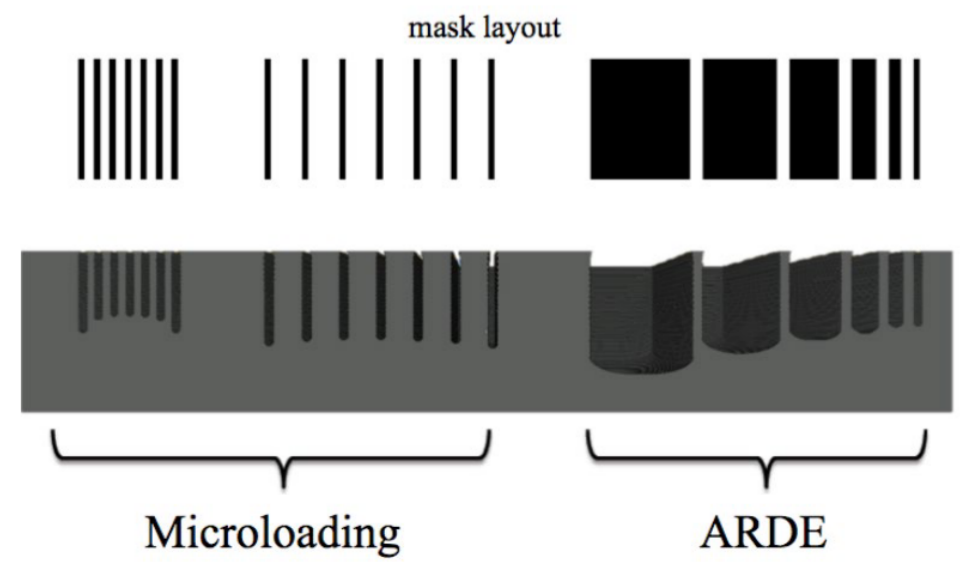

微观负载效应指晶圆表面小尺度的刻蚀速率差异,由局部未掩模密度不均和深宽比相关刻蚀(ARDE/RIE 滞后,高 AR / 窄沟槽刻蚀更慢)共同导致。

这一小节最重要的就是下面这张图,可以说是必考,图一定要会画,而且还要记住分别是什么名称:

观察上图,可以发现,挨得越近,刻得越浅;而线条越细,会导致气体不易进去,则一样刻得浅。

5 互连技术(Interconnect Technology)

互连线将芯片上的电子电路连接起来,以实现正常功能。

5.1 铝互连

优点:

- Ease of deposition

- Dry etching

- Does not contaminate

- Ohmic contacts to

- Excellent adhesion to dielectrics

缺点:

- Electromigration

- Hillocks

- Higher resistivity (relative to

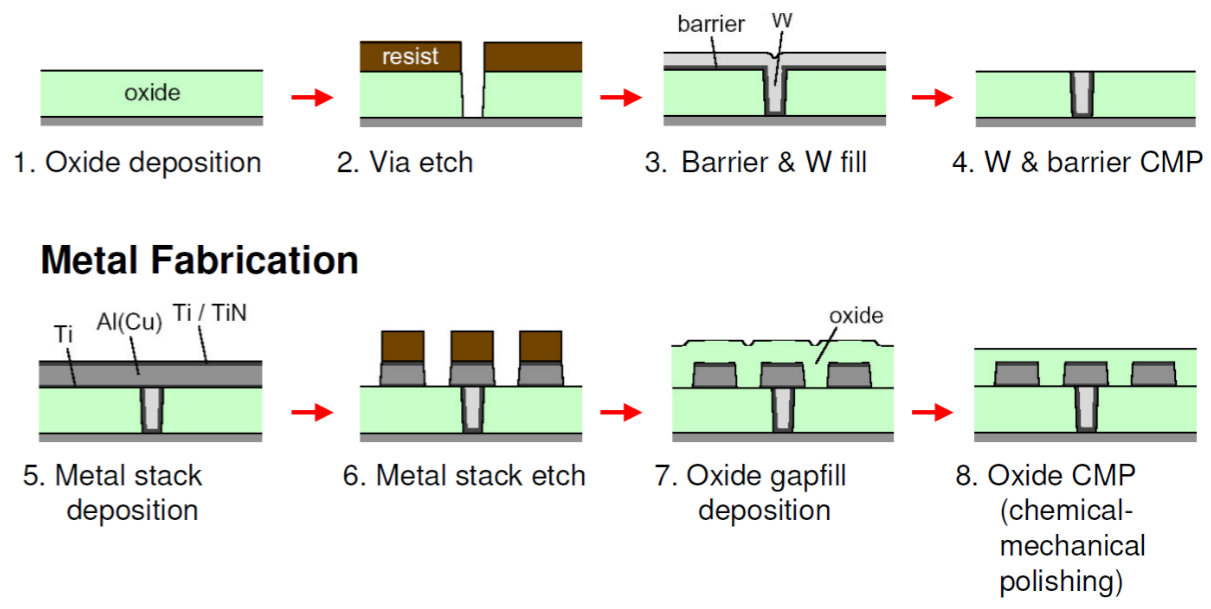

5.1.1 铝互连技术过程

着重关注第五步和第六步,先是金属堆叠沉积,也就是依次沉积 Ti/TiN 阻挡层、Al (Cu) 金属层、Ti/TiN 覆盖层;然后进行金属堆叠刻蚀,光刻 + 干法刻蚀,刻出铝导线的图形。

5.1.2 铝互连的问题

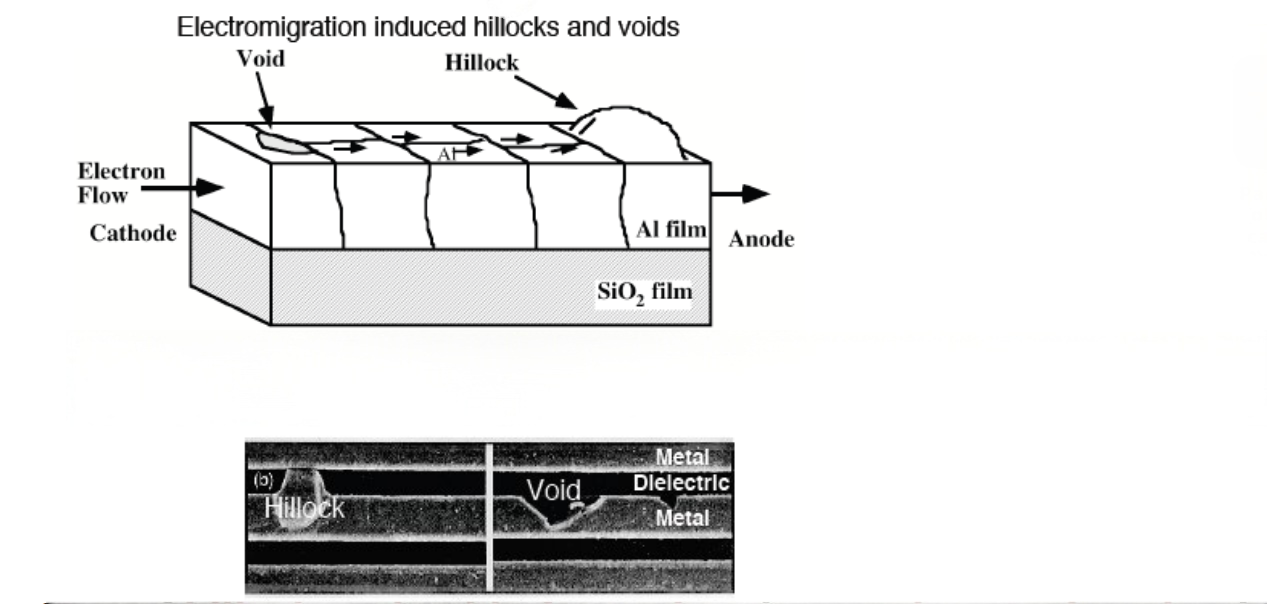

5.1.2.1 电迁移

电迁移是电子风(electron wind)驱动铝原子沿晶界(grain boundaries)扩散的现象:

- 电子从阴极流向阳极,高速运动的电子会撞击铝原子,将动量传递给铝原子;

- 铝原子沿电子流动方向(从阴极到阳极)扩散,最终在导线中形成空洞(Void)和小丘(Hillock)。

下方的SEM 图就是实际铝互连导线中电迁移导致的小丘和空洞的微观形貌。

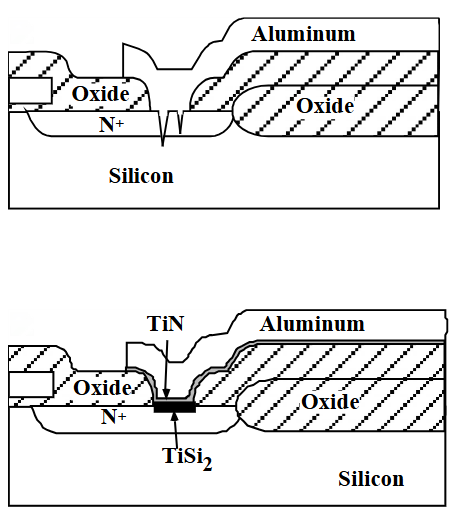

5.1.2.2 铝互连中产生的尖峰(Spiking)问题

在

有两种方案解决该问题:

-

-

阻挡层法:在铝与硅之间插入

5.2 铜互连

优点:

-

-

-

缺点:

-

-

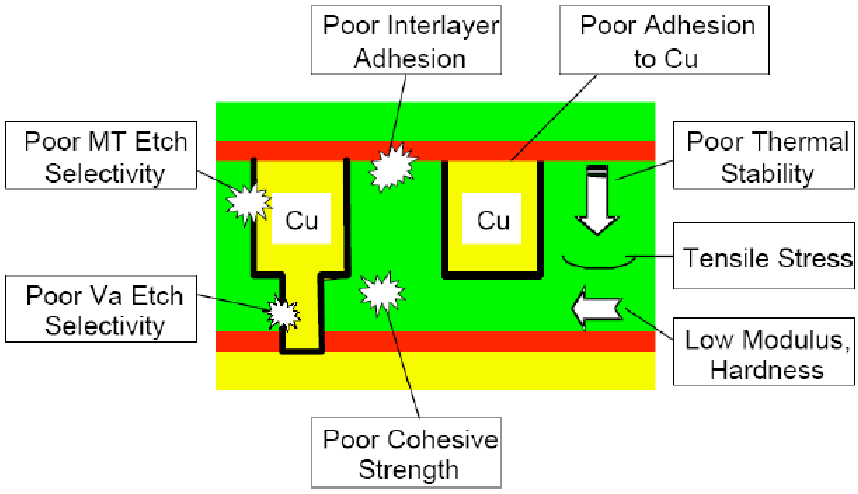

5.2.1 铜互连的问题

- 铜难以干法刻蚀:无法像铝那样通过干法刻蚀直接形成导线图形,传统刻蚀工艺不适用;

- 铜在硅和氧化硅中扩散极快:会导致结漏电增加、载流子寿命降低、结击穿电压下降,严重劣化器件性能。

对应的解决方案:

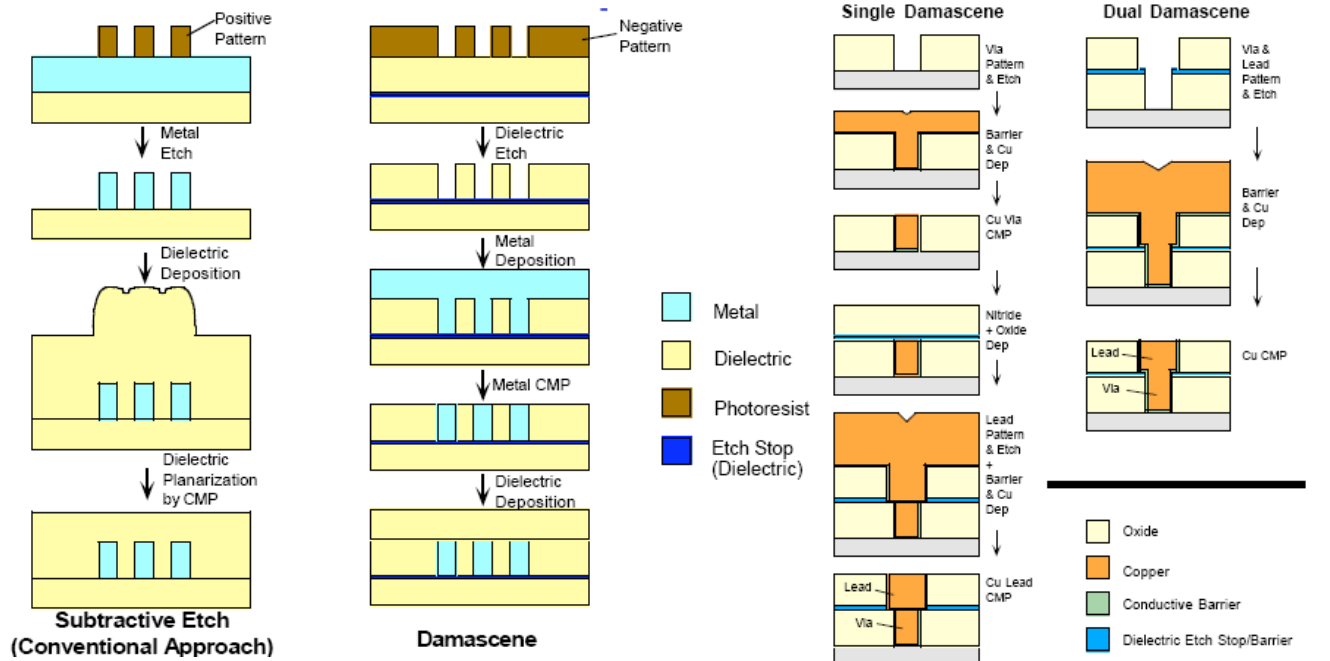

- 大马士革(镶嵌,Damasceme)工艺:先在介质层中刻出沟槽/通孔,再填充铜,最后通过 CMP 抛光形成互连,绕开了铜难以刻蚀的问题;

传统的工艺是先Deposite,然后再Etch;大马士革工艺是先Etch,然后再CMP。

- 扩散阻挡层封装(Encapsulate):用阻挡材料(如

其中,方法2中阻挡层的材料主要有四类,分别是:

- 过渡金属单质(Transition metals)

- 过渡金属合金(Transition metal alloys)

- 过渡金属化合物(Transition metal - compounds)

- 非晶三元合金(Amorphous ternary alloys)

同时还需要知道两种沉积阻挡层的工艺(了解即可):

- PVD(物理气相沉积,比如溅射):

- ALD(原子层沉积)

5.2.2 铜的沉积方法

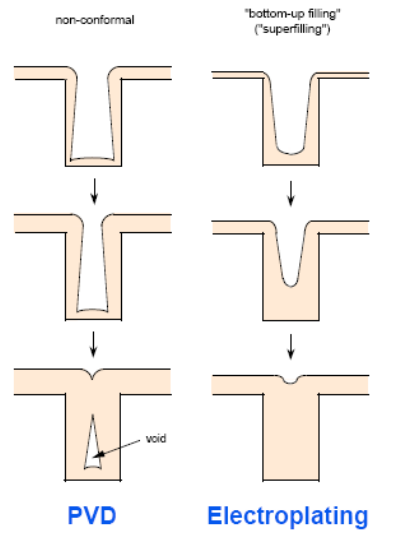

- 物理气相沉积(PVD)

- 优点:可制备强 (111) 织构、表面光滑的铜膜;

- 缺点:台阶覆盖性差(step coverage),在高深宽比沟槽/通孔中会发生 “夹断(Pinching)”,无法实现无空洞填充,不适合先进制程。

- 化学气相沉积(CVD)

- 优点:台阶覆盖性极佳,可在高深宽比结构中实现保形沉积;

- 缺点:工艺和维护成本高,制备的铜膜 **(111) 织构弱、晶粒细、表面粗糙 **,电迁移性能劣于 PVD 铜膜。

- 铜电化学沉积(EVD)

- 填充能力拉满:台阶覆盖和填充能力和 CVD 一样;

- 兼容 low-K 介质;

- 铜膜性能优异;

- 超大晶粒,抗电迁移拉满:通过自退火(Self-Annealing)(镀完铜在室温下自动晶粒长大,无需额外高温),能长出比 PVD/CVD 大得多的铜晶粒,晶界大幅减少,电迁移寿命大幅提升。

下面的图要求一定要会画:

Copper electroplating needs a thin copper seed layer first, as copper cannot grow directly on insulating dielectric surfaces. The seed layer’s texture and surface roughness fully control the final plated copper’s quality: a smooth, strongly (111)-textured, thin PVD seed layer produces a high-performance plated copper layer with strong (111) texture and large grains (ideal for reliable chip interconnects).

中文对照:电镀铜首先需要一个薄的铜籽晶层,因为铜不能直接在绝缘电介质表面生长。籽晶层的纹理和表面粗糙度完全控制了最终镀铜的质量:光滑、具有强(111)纹理的薄PVD籽晶层可产生具有强(110)纹理和大晶粒的高性能镀铜层(非常适合可靠的芯片互连)。

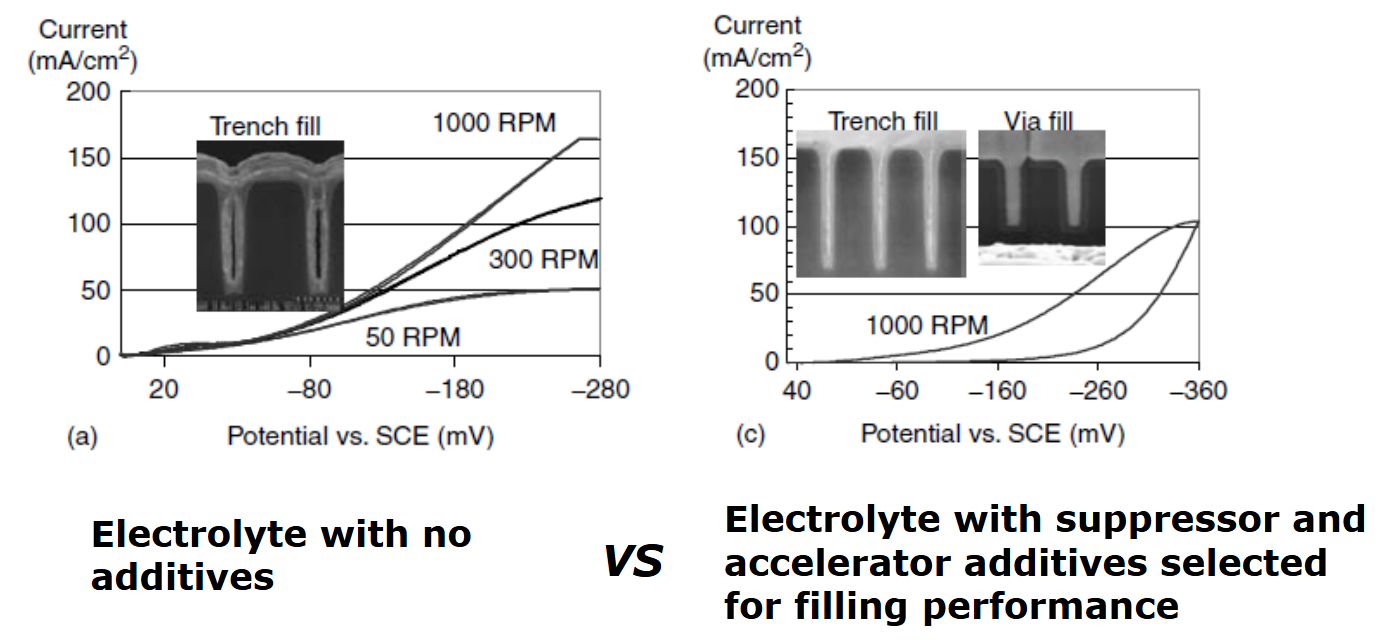

5.2.3 The effects of additives

5.2.4 铜导线电阻率的影响

As copper interconnects shrink in advanced chips, the high-resistivity diffusion barrier (which can’t be thinned below a minimum thickness) takes up a larger share of the wire’s cross-section. This reduces the effective copper area, significantly increasing the overall resistivity of the composite wire far above bulk copper’s value.

中文对照:随着铜互连尺寸不断缩小,高阻的铜扩散阻挡层无法无限减薄,导致其在导线截面积中的占比越来越大,最终大幅提升了复合铜导线的整体电阻率,严重限制了先进制程铜互连的性能。

Practice:

Explain why resistivity increases as line width decreases. Also, explain the difference in resistivity behavior between lines with pure metal and those with barrier.

Answer:

- Resistivity increases as line width decreases as a result of enhanced surface and grain boundary scattering;

- In the case of lines with pure metal and barrier, the effective resistivity is higher because barrier material usually has higher resistivity and it scales slower.

5.3 Future of interconnect technology

记住下面三个名词即可,考试只会考名称:

- Optical interconnect

- RF interconnect

- 3D interconnect

6 晶圆清洗技术

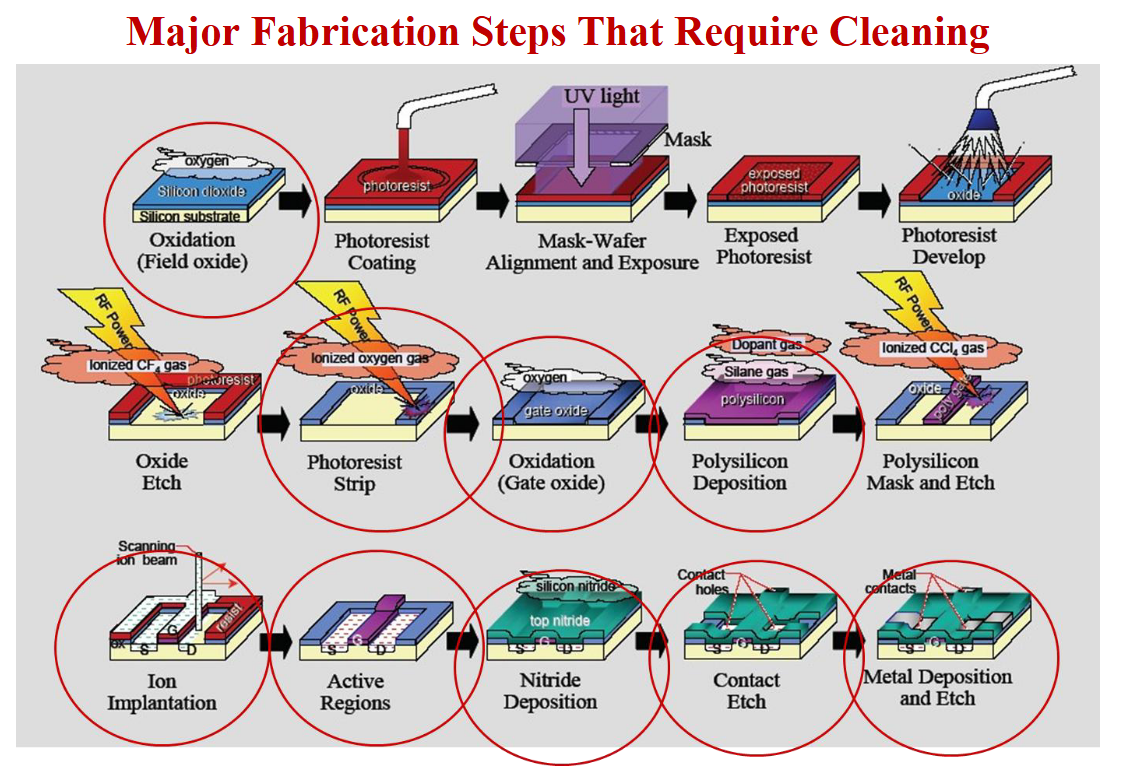

晶圆清洗及表面处理的目的(objective)是: removal of particle and chemical impurities from the semiconductor surface without damaging or deleteriously altering the substrate surface.

在 0.18 微米设计规则下,约 400 道总工序中有 80 道为清洗工序。

凡是在晶圆表面做增材工艺(additive,往晶圆上镀 / 生长薄膜、涂材料),或是减材工艺(subtractive,从晶圆上刻蚀、去掉材料)的步骤都必须做晶圆清洗。

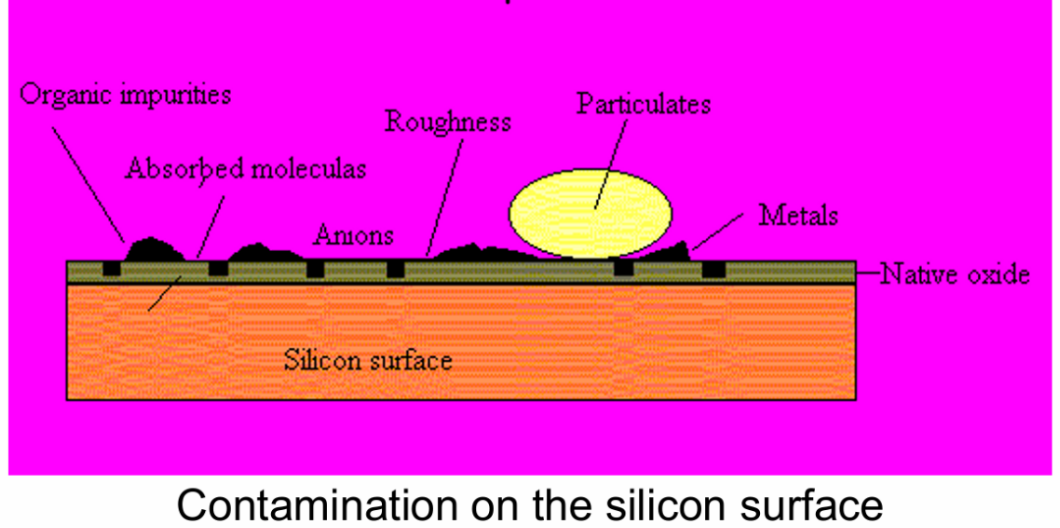

6.1 晶圆表面主要的污染物

晶圆表面的污染物主要可分为五类:

-

Particles(颗粒污染物)

-

Metallic Impurities(金属杂质)

-

Organic Contamination(有机污染物)

-

Native Oxides(自然氧化层)

-

Electrostatic Discharge(静电放电,ESD)

6.1.1 Particles(颗粒污染物)

-

吸引力(Attractive Forces, AF)

这是让颗粒牢牢吸附在晶圆表面的力,分为两种:

- 范德华力(van der Waals forces):short range

- 静电吸引力(Electrostatic):当颗粒携带的电荷,和晶圆表面的电荷是异性电荷时,就会产生长距离的静电吸引力。

-

排斥力(Repulsive Forces, RF)

这是能让颗粒脱离晶圆、实现清洗的核心力,同样分为两种:

- 静电排斥力(Electrostatic):当颗粒和晶圆表面带同种电荷时,就会产生静电排斥力,把颗粒从晶圆表面推开。

- 空间位阻力(Steric forces): due to absorbed polymer layers on the surface of the particles and wafer

When AF > RF, particle deposition is favorable.

要能解释 why there’s particals(背一背红色部分就行):

-

Adsorption of

原理:晶圆表面的二氧化硅(

- 酸性溶液中:Si-OH 会吸附

- 碱性溶液中:Si-OH 会失去

- 酸性溶液中:Si-OH 会吸附

-

Selective adsorption of positive or negative ions (hydrophobic materials)

原理:疏水材料(最典型的就是光刻胶、有机污染物)的表面不会和水反应形成羟基,但会从清洗液中,选择性地吸附正离子或者负离子,从而让自身带上电荷。

-

Ionization of surface groups (polymers such as nylon)

它和第一种 “离子吸附” 的核心区别是:它不需要从溶液里吸附离子,靠材料自身的表面基团就能电离带电。

原理:聚合物(光刻胶、有机污染物、设备的高分子部件)的表面自带可电离的化学基团,比如羧基(

- 羧基会电离出

- 氨基会结合

- 羧基会电离出

-

Fixed charges in the matrix structure exposed due to counter ion release

原理:晶体材料、离子型聚合物的晶格/分子结构里,本身就带有固定的正/负电荷,平时被带相反电荷的反离子平衡,整体呈电中性;当这些反离子释放到溶液中后,材料本身的固定电荷就会暴露,让表面带上稳定的固定电荷。

6.1.2 金属杂质(Metallic Impurities)

金属杂质分为两大类,均会对半导体器件造成不可逆的性能损伤:

| 杂质类型 | 核心元素 | 主要危害 |

|---|---|---|

| 碱金属 | Sodium(Na)、Potassium(K)、Lithium(Li) | 极易在栅氧层中迁移,导致栅氧漏电、器件阈值电压漂移,破坏 MOS 器件的核心特性 |

| 重金属 | Iron(Fe)、Copper(Cu)、Aluminum(Al)、Chromium(Cr)、Tungsten(W)、Titanium(Ti) | 在硅中形成深能级陷阱,降低载流子寿命,导致 pn 结漏电,严重时会造成器件完全失效 |

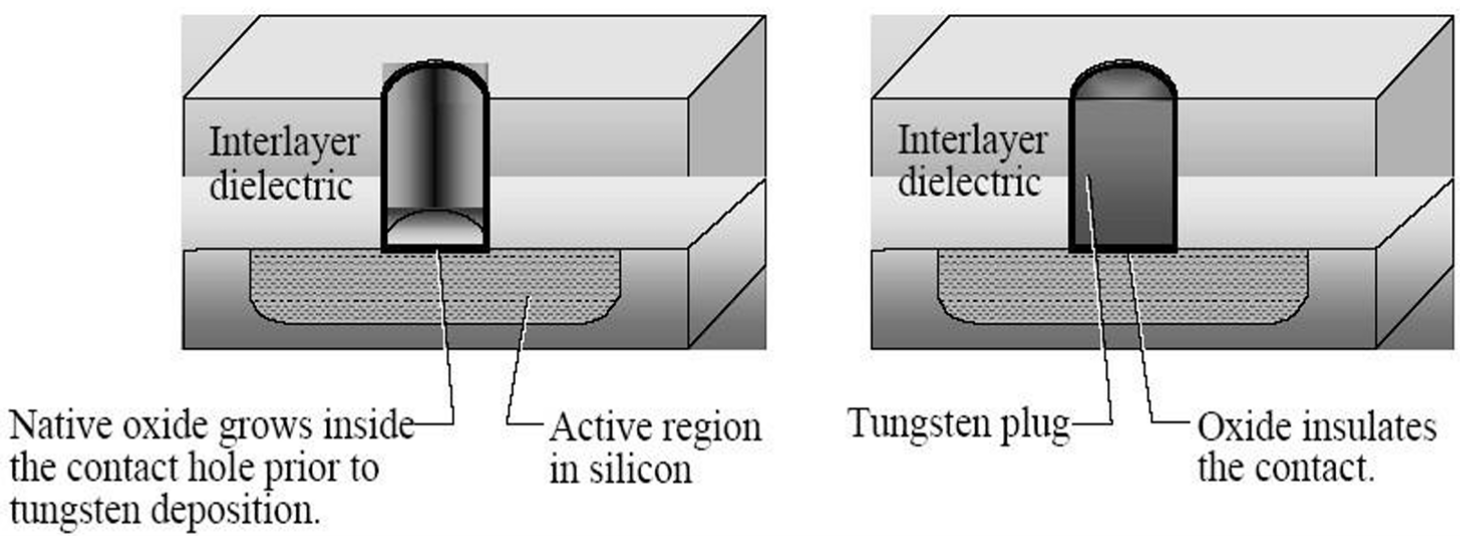

6.1.3 接触孔处的自然氧化层(Native Oxide on Contacts)

Native oxide lines the bottom of the contact hole, creating poor electrical contact between tungsten and the doped silicon region.

需要区分 3 种氧化的速率,以此理解自然氧化的特点:

- 1-2 nm thickness:自然氧化层的厚度只有 1-2 纳米,极薄,肉眼完全不可见,但足以毁掉电接触。

- Dry oxide tens of nm per hour:干氧氧化(工艺里可控、有目的生长栅氧、场氧的干法氧化工艺),生长速率是每小时几十纳米,比自然氧化快得多。

- Wet oxide several um per hour:湿氧氧化,生长速率是每小时几个微米(1μm=1000nm),是三者里最快的,用来生长厚的场氧绝缘层。

自然氧化是不可控、非故意、有害的污染物;而干氧 / 湿氧是我们工艺里可控、有目的、功能性的氧化层,二者完全不是一回事。

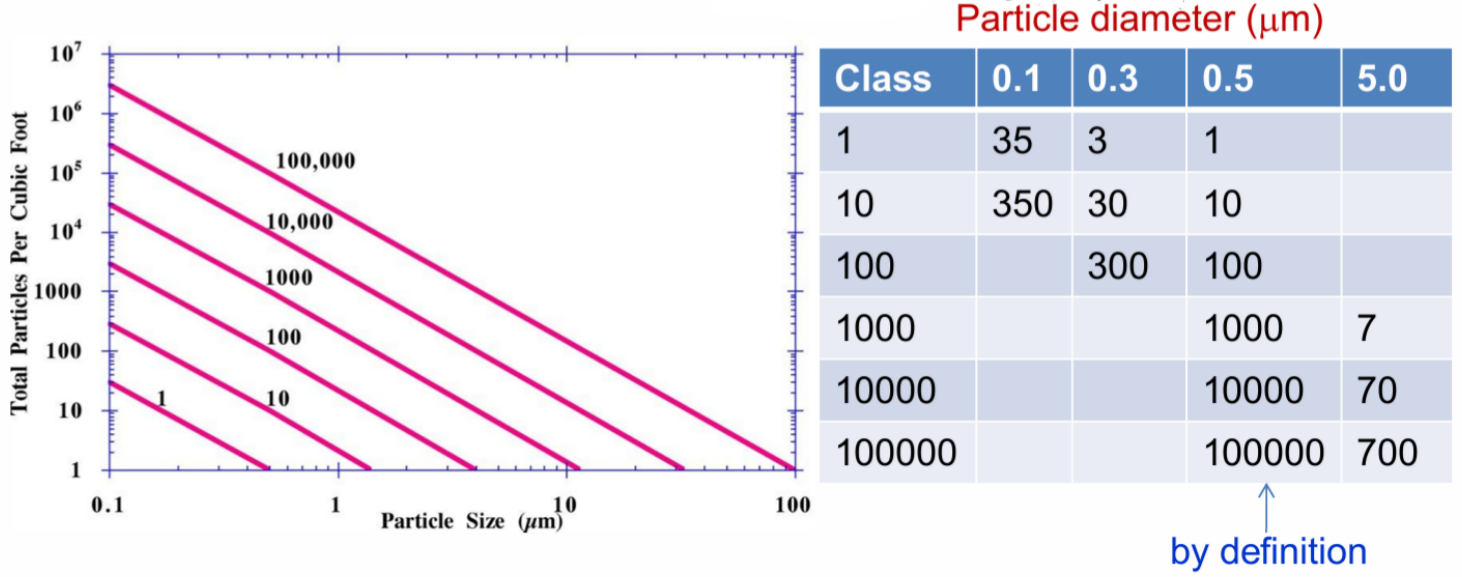

6.2 Clean Room

只需要记住无尘服(Bunny suits)

另外要知道为什么洁净室是黄色的?

黄光可以防止光刻胶被环境光提前曝光,避免图形报废。

10nm – 10μm 是对芯片良率危害最大的颗粒尺寸区间,也是洁净室管控的核心。

颗粒污染晶圆的 2 种沉积机制

- 布朗运动(Brownian motion):对于粒径 < 0.5μm 的小颗粒,这是最主要的沉积方式。

- 重力沉降(Gravitational sedimentation):对于更大的颗粒,主要靠重力自然掉落到晶圆表面,也就是上面说的 > 10μm 的颗粒会快速沉降的原理。

红框内的Class列是洁净等级,0.5μm这一列,就是洁净等级的官方定义标准,Class 1 对应 1 个、Class 10 对应 10 个、Class 10 万对应 10 万个。

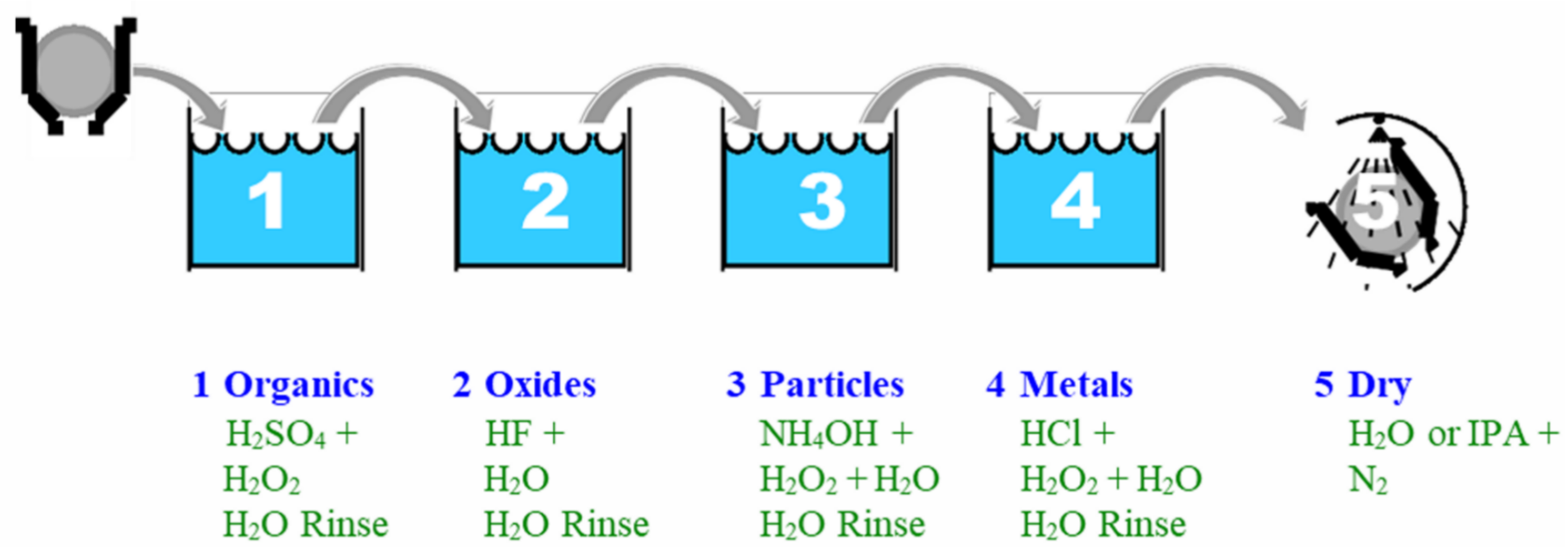

6.3 现代晶圆清洗(Modern Wafer Cleaning)

晶圆清洗的本质,就是从晶圆表面彻底去除颗粒污染物、有机污染物、金属杂质。

-

三类污染物的对应去除方案

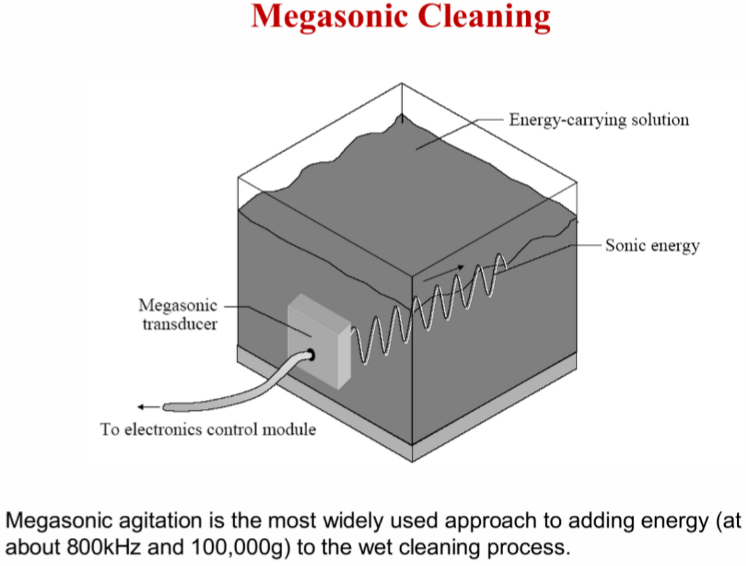

污染物类型 主流去除技术 particals ultrasonic/megasonic agitation(超声/兆声搅拌) Organics(photoresist) ① remove metals and any remaining organics RCA 清洗

6.3.1 光刻胶去胶(Resist Strip)

光刻胶通过灰化(ashing)去除,也就是光刻胶可被 plasma 烧成灰去除,这是一种等离子体工艺,本质是在真空环境中,用氧气等离子体 “燃烧” 掉晶圆表面的光刻胶:高活性氧自由基与有机光刻胶发生氧化反应,将高分子聚合物分解为气态小分子,被真空泵抽走,实现光刻胶的高效去除。

而灰化过程只能去除有机的光刻胶本体,会把这些金属、无机杂质全部浓缩、残留在晶圆表面,因此干法灰化之后,必须配套一道湿法清洗工序。

6.3.2 典型的清洗流程

总共有五步:

step 1: 去除有机污染物(Organics)

- 核心溶液:

- 工艺原理:(Acid + Oxidizing) remove organics,利用强氧化性将光刻胶、有机残留等高分子污染物彻底碳化、分解,转化为可溶于水的小分子物质去除。

step 2: 去除氧化层(Oxides)

- 核心溶液:

- 工艺原理:(F + Acid + Oxidizing) remove SiO2,氢氟酸是唯一能在常温下与二氧化硅(

step 3: 去除颗粒污染物(Particles)

- 核心溶液:

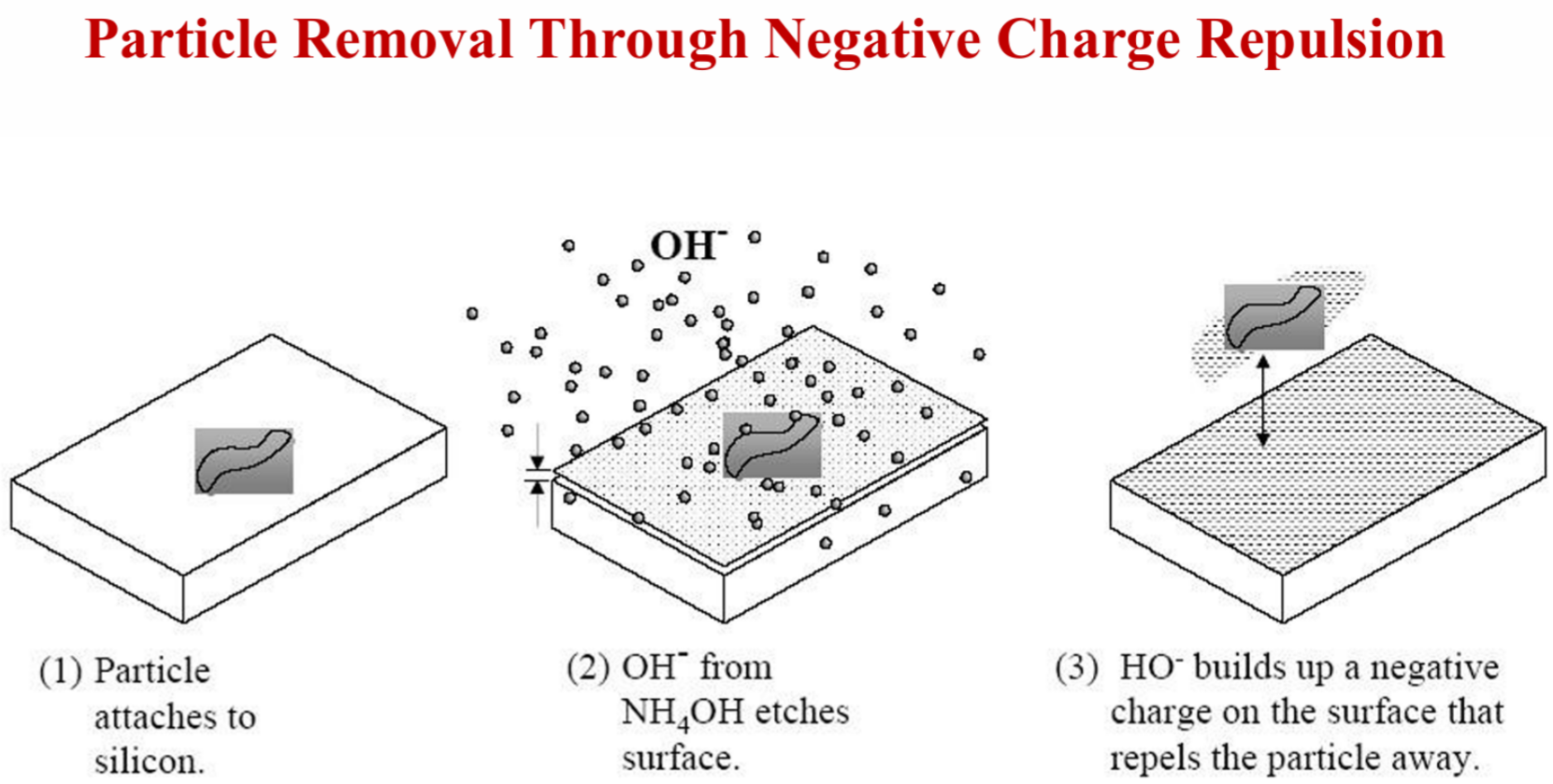

- 工艺原理:碱性环境下,过氧化氢会氧化硅表面形成极薄的氧化层,氨水以极低速率轻微蚀刻氧化层,从颗粒底部完成 “底切”,让颗粒脱离晶圆表面;同时氨水会让晶圆和颗粒表面同时带上负电,通过静电排斥力让脱离的颗粒无法再次吸附到晶圆上。

step 4: 去除金属杂质(Metals)

- 核心溶液:

- 工艺原理:盐酸和过氧化氢会将晶圆表面的碱金属(钠、钾等)、重金属(铁、铜、铝等)杂质,转化为可溶于水的稳定金属氯化物,彻底从晶圆表面清除。

step 5: 晶圆干燥(Dry)

- 核心方案:

DI water(Deionized water, 超纯水) needed in All Steps,每一步化学清洗结束后,都必须用超纯水对晶圆进行彻底漂洗(Rinse)。把前序的化学溶液、溶解的杂质完全冲干净,才能进入下一个清洗槽,避免交叉污染、化学残留导致晶圆二次污染。

生产 1 加仑的超纯水,需要消耗 4-6 加仑的自来水。

6.3.3 湿法清洗中的化学物质

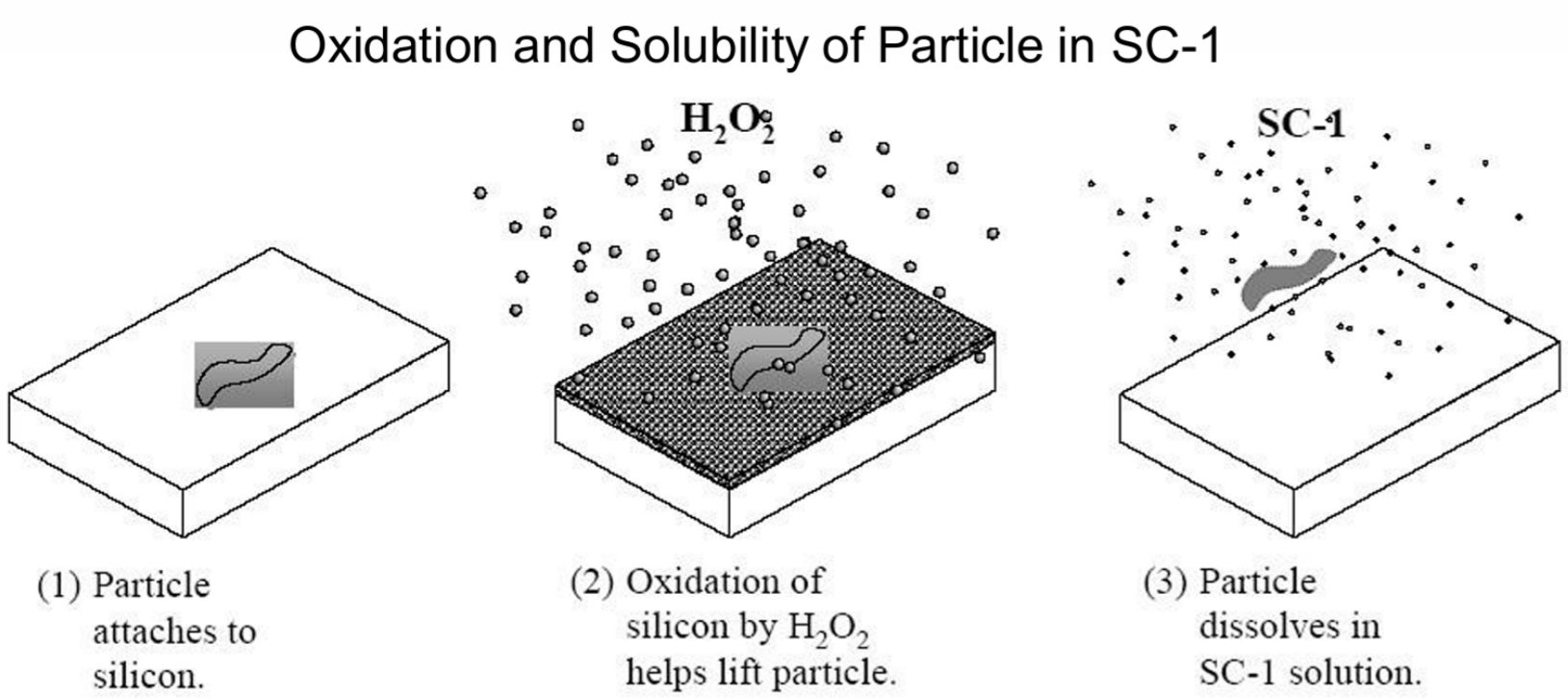

APM 全称 Ammonia Peroxide Mixture,即氨水-过氧化氢混合液,也叫SC-1(Standard Clean 1),主要用途是particle removal。

下面两个问题决定了清洗的良率与晶圆是否报废:

-

Can also result in surface roughening(晶圆表面粗糙化)

-

Presence of the oxidant is critical(氧化剂(过氧化氢)的存在是核心关键):If lost,solution will etch silicon.

SC-1去除晶圆颗粒的两个机制一定要会自己解释,也就是下图的文字部分:

6.4 先进晶圆制程中的清洗工艺

-

Front-End Of-Line(FEOL):Individual devices are patterned in the semiconductor wafer

- Pre-Diffusion Cleaning(扩散前清洗)

- Post Photolithography Photoresist Removal and Cleaning(光刻后光刻胶去除与清洗)

- Post Gate Etch Photoresist Removal and Cleaning(栅极蚀刻后光刻胶去除与清洗)

- Post Ion Implant Photoresist Removal and Cleaning(离子注入后光刻胶去除与清洗)

- Post Shallow Trench Isolation (STI) CMP Cleaning(浅沟槽隔离 CMP 后清洗)

-

Back-End-Of-Line(BEOL):Individual devices are interconnected with wiring on the vvafer

- Pre Thin-Film Deposition Cleaning(薄膜沉积前清洗)

- Post Contact and Via Etching Cleaning(接触孔与通孔蚀刻后清洗)

- Post Metal Etching Photoresist Removal and Cleaning(金属蚀刻后光刻胶去除与清洗)

- Post Metal and Low-k Dielectric CMP Cleaning(金属与低 k 介电材料 CMP 后清洗)

一定要知道如何区分 FEOL 和 BEOL :

- 只要清洗工序和晶体管、栅极、掺杂、器件隔离等芯片本体制备相关,全部属于FEOL 前道;

- 只要清洗工序和金属布线、接触孔/通孔、互连薄膜沉积相关,全部属于BEOL 后道

6.4.1 晶圆湿法清洗的辅助工艺

-

Megasonic Cleaning

-

Water Rinsing

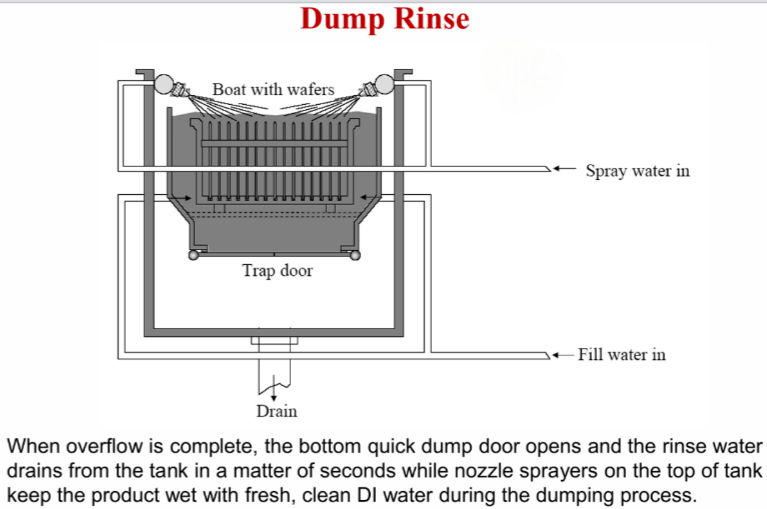

超纯水持续流过晶圆表面,形成连续冲刷,带走表面残留。漂洗合格的判定标准就是通过测量漂洗出水的电阻率,超纯水的电阻率对离子杂质极其敏感,只要水中含有微量离子残留,电阻率就会急剧下降。

漂洗方案:

-

倾倒式漂洗(Dump rinsing):专门用于亲水表面的晶圆;

-

热水漂洗(Hot water):可用于部分工艺后的漂洗,但绝对禁止用于氢氟酸(HF)处理后的晶圆表面,HF 处理后硅表面为疏水状态,热水会导致水膜分布不均,产生水印与二次污染。

-

-

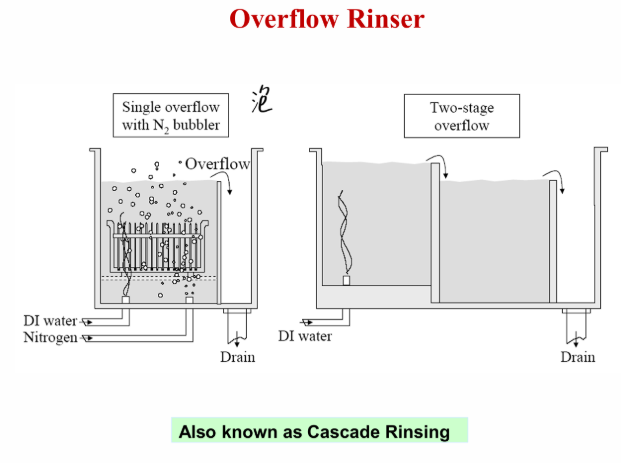

Overflow Rinser

6.5 Drying

这一步的目标是 remove as much of the water as possible,避免水中的微量杂质在水分蒸发后留在晶圆表面,形成水印、颗粒残留,造成致命的二次污染,对应你手写注释的 “去除尽可能多的水”。

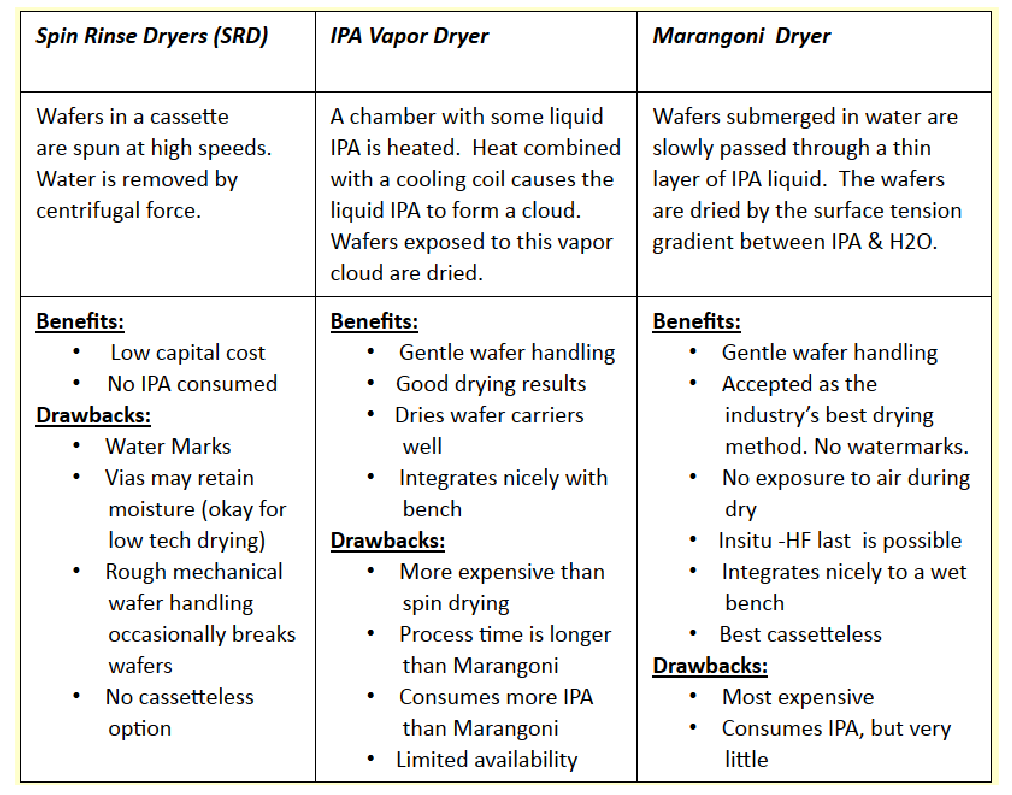

主要有两个主流的干燥技术:

-

Spin Rinse Dryer, SRD(旋转漂洗干燥机)

将晶圆放入专用卡匣中,以数千 RPM 的转速高速旋转,通过离心力将晶圆表面的水分彻底甩出;同时配合热高纯氮气吹扫(Hot

-

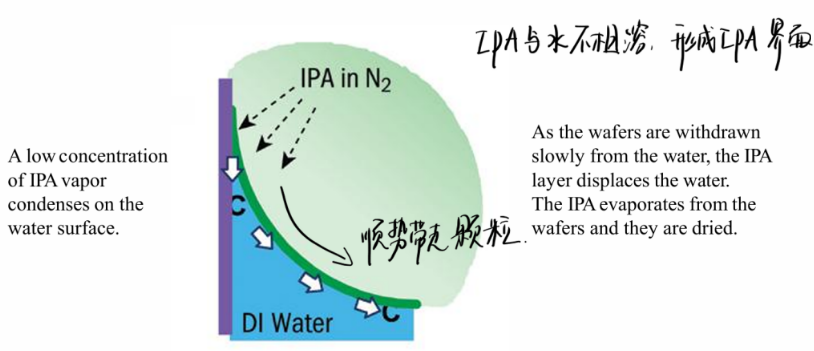

IPA Vapor Drying(异丙醇蒸汽干燥)

用 IPA 蒸汽置换晶圆表面的水膜,主要有三种实现方式:

-

Tank

-

Vapor jet, VJD(蒸汽喷射式 IPA 干燥)

-

-

Marangoni-type(马兰戈尼型干燥)

7 化学机械平坦化(CMP)

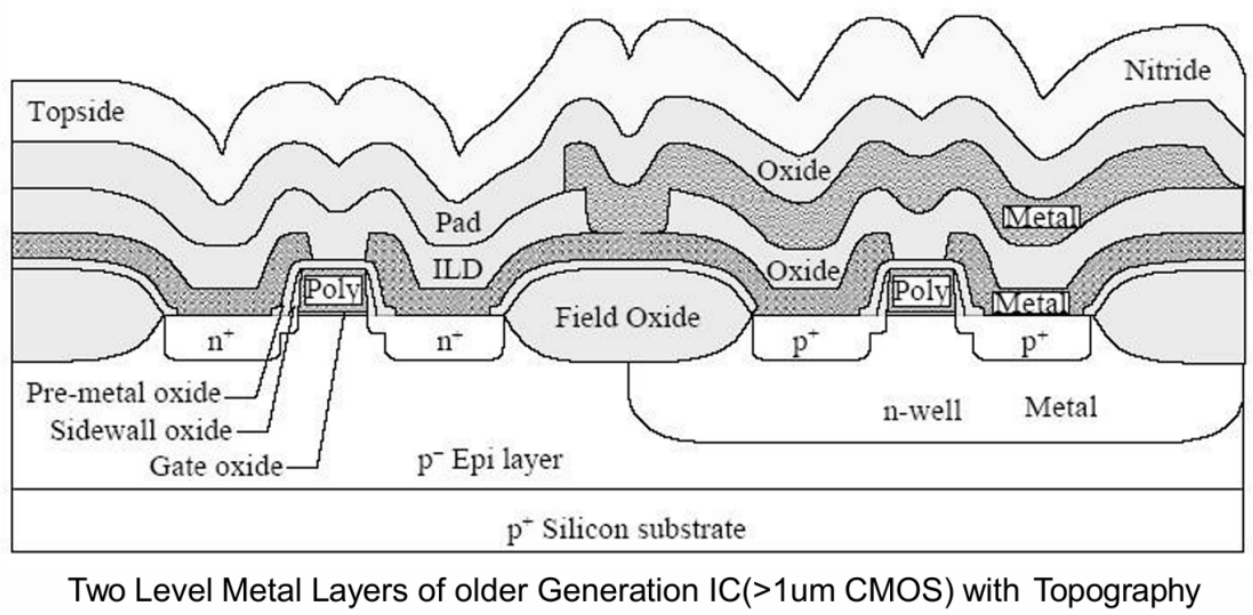

芯片的器件关键尺寸持续缩小,但芯片内的互连线总长度却在飞速增长,最终导致晶圆表面出现严重的高低不平的非平面台阶形貌。

互连线层数越多,晶圆表面的台阶就越高、形貌越不平坦;而器件关键尺寸缩小后,光刻的景深(DOF)会急剧变小,这种非平面的台阶会直接导致:

- 光刻无法同时聚焦台阶的顶部和底部,图形失真、线宽失控;

- 台阶处的光线反射,造成光刻胶图形缺口缺陷;

- 台阶处的薄膜沉积厚度不均,导致互连线断路、短路。

7.1 非平面金属化

7.1.1 累积效应

图中是一包含两层金属互连结构。可以清晰看到:

- 最底部的硅衬底(Si substrate)原本是极致平整的;

- 但经过栅极制备、氧化层/金属层沉积、图形化蚀刻等工艺后,晶圆表面形成了波浪状、高低起伏的台阶形貌,也就是非平面拓扑结构;

- 仅两层金属互连,就已经形成了明显的起伏,而先进制程芯片的金属互连层数可达 10 层以上,形貌的不平坦会被持续放大。

晶圆表面的非平面性是累积形成的,从最初平整的硅晶圆开始,每一步工艺都会加剧不平坦,主要是因为:

- 晶圆全域的薄膜沉积厚度不均匀;

- 栅极、互连线、接触孔等 IC 图形化结构带来的固有台阶形貌。

7.1.2 光刻工艺失效

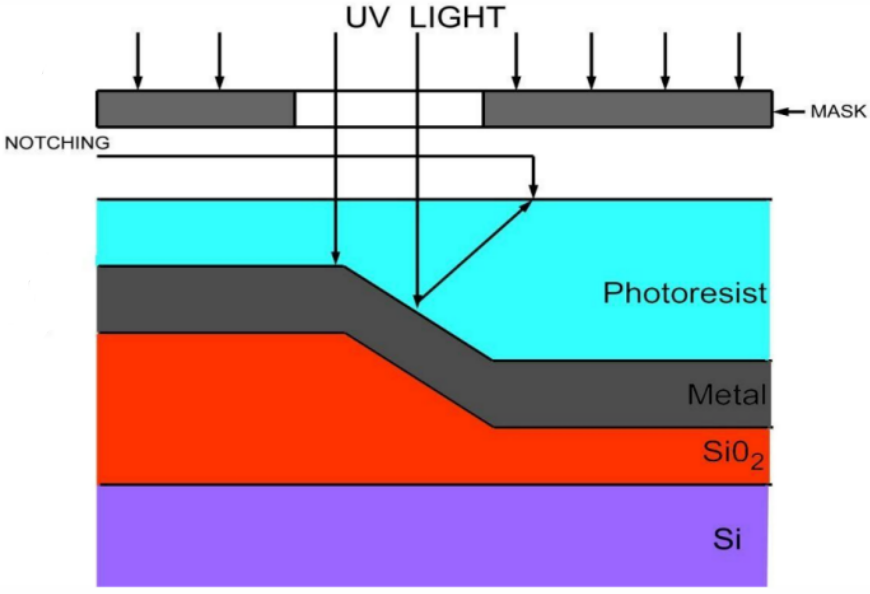

(1) 不平坦的表面会彻底破坏光刻工艺的精度,甚至让光刻完全失效。

主要是以下三个问题:

-

Depth of Focus (DOF)

-

Light reflection at steps causing notching

-

Resist thickness variation over steps

平坦化表面对光刻的优势:

- Lower Depth-of-Focus requirement

- Reduced optical reflection effects on resist profiles

- Reduced resist thickness variation over steps

- Better dimension control

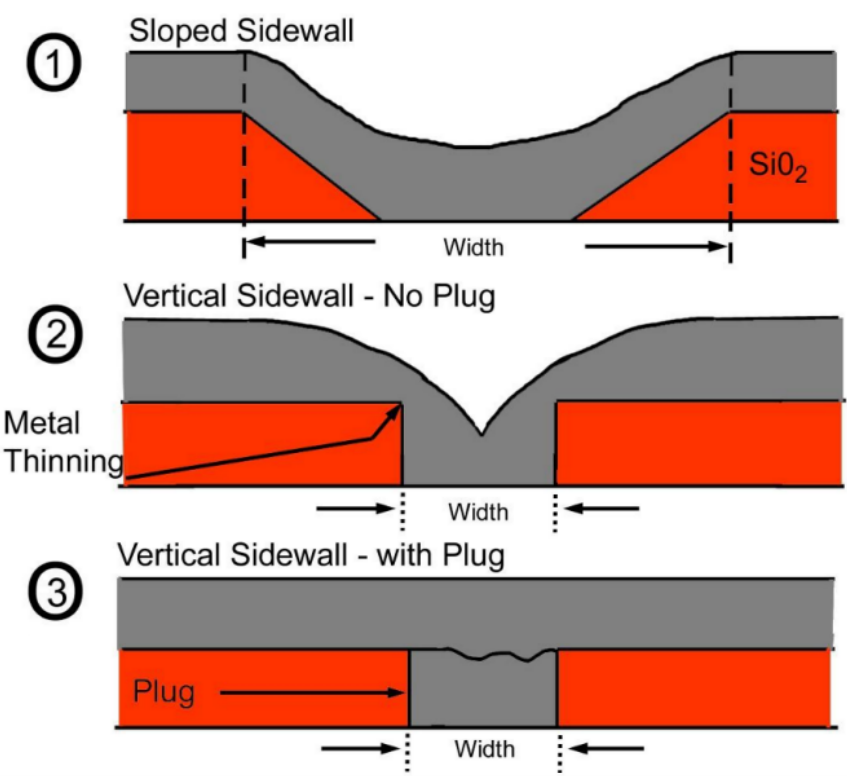

(2) 不平坦的表面会导致金属互连线的台阶覆盖不良,引发电路失效。

主要问题是金属台阶覆盖不良与变薄

非平面的台阶形貌,会让金属沉积时出现严重的厚度不均:

- 缓坡台阶(①):金属层在侧壁已经出现明显变薄,厚度均匀性极差;

- 陡直台阶(②x):先进制程的台阶是接近 90° 的陡直侧壁,金属沉积时,在台阶底部的拐角处会出现极端的变薄,甚至出现缝隙、空洞,直接导致互连线断路;同时,变薄的区域电阻会急剧升高,还会大幅加剧电迁移效应(金属原子在电流作用下移动,长期工作后互连线会断路),严重缩短芯片寿命。

通过图 ③ 中CMP 平坦化,配合大马士革工艺,在介质层中刻出沟槽/通孔,填充金属后再用 CMP 磨平,形成垂直的金属插塞(Plug)。

7.2 Chemical Mechanical Planarization (CMP)

7.2.1 CMP的定义和流程

Chemical Mechanical Planarization, CMP(化学机械平坦化),是一个physical-chemical process ,目标是为了让晶圆表面实现 locally and globally flat。

CMP中的两大反应:

-

化学反应

- hydroxyl(OH) ions attack

- oxidants enhance metal dissolution and control passivation in metal CMP

- hydroxyl(OH) ions attack

-

机械作用

polisher rotation and pressure

化学作用与物理作用相结合,去除晶圆表面的结构:

若仅依靠机械作用→会产生scratches

若仅依靠化学作用→效果 same as wet etching

为什么必须用 CMP?

- 为先进器件提供precise photolithography

- 支撑advanced multilevel metallization process

另外还需要记住CMP 工艺的两个评价指标:

| 指标 | 全称 | 定义与公式 | 核心意义 |

|---|---|---|---|

| NU | 抛光后非均匀性(Post-polish Nonuniformity) |

|

CMP 工艺的核心管控指标,数值越小,代表晶圆全域的抛光厚度越均匀,良率越高;它由晶圆局部去除速率的波动导致。 |

| RR | 去除速率(Removal Rate) |

|

决定 CMP 设备的产能,同时和抛光均匀性、平坦化效果存在天然的权衡关系。 |

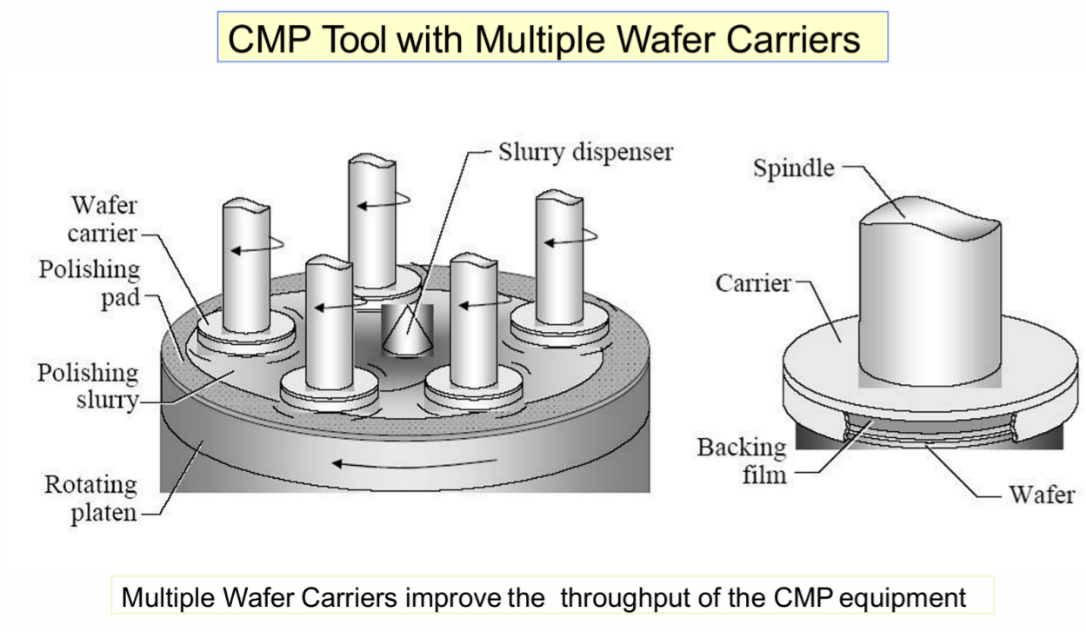

7.2.2 CMP设备组件

有几个比较重要的组件要会分辨,并知道其作用:

- 背衬膜(Backing Film): provides elasticity between carrier and wafer

- 抛光平台(Rotating Platen):负责固定Polishing Pad(通常由polyurethane材质制成,厚度约 1mm),主要用来rough surface to hold slurry。

- 研磨液分配器(Slurry Dispenser):持续均匀地向抛光垫表面提供Slurry,保证化学与机械作用的稳定进行。

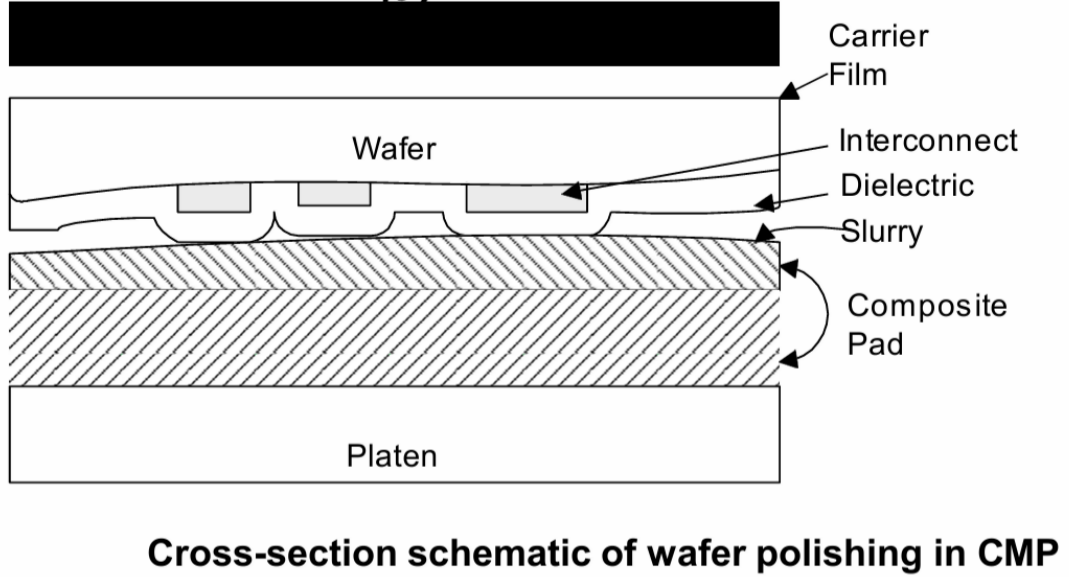

7.2.2.1 Polishing Pad

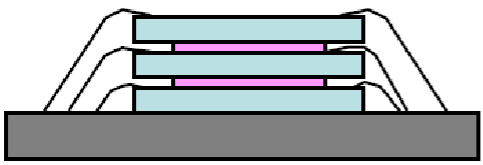

如上图剖面图:

Polymer polishing pad is pressed against the wafer surfface. (聚合物抛光垫被压向晶圆表面)

Pad serves to transport the slurry to the wafer and providee pressure. (抛光垫用于将研磨液输送至晶圆并施加压力)

Both pad and wafer rotate in opposite directions. (抛光垫与晶圆沿相反方向旋转)

The pad is an expensive consumable in the CMP processs. (抛光垫是一种成本较高的消耗品)

7.2.2.2 Slurry

pad never actually touches the wafer。(抛光垫实际上永远不会直接接触晶圆表面)

晶圆与抛光垫之间,始终填充着一层持续流动的研磨液,所有化学与机械作用都通过研磨液完成。

- slurry for polishing oxide films is alkaline (

- slurry for polishing metal films is acidic (

Chemical action of slurry changes top monolayers(单原子层) of film into soft material that is easily removed by motion of abrasive particles(易被磨料颗粒),也就是先化学物软化表面,再由磨料去除。针对不同的抛光材料,化学软化的路径不同:

- 氧化物薄膜:表面发生水合反应(hydrated),

- 金属薄膜:表面发生氧化反应(owidized)

7.2.3 CMP工艺的特性

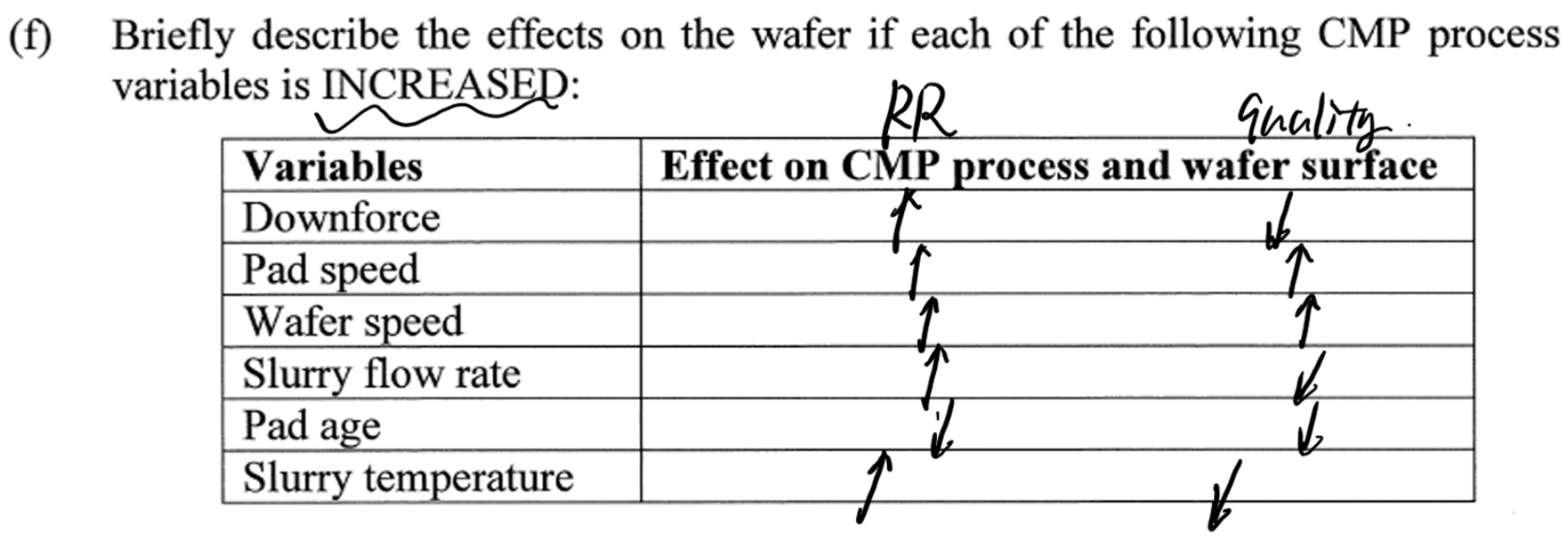

这部分一般就是给个表格让判断值升高还是下降。

(1) 去除速率(Removal Rate, RR)

去除速率的单位为微米 / 分钟,行业典型值为 1-3μm/min。计算公式为:

其中:

- k:由待抛光材料的硬度 / 杨氏模量、研磨液配方、抛光垫特性共同决定,固定工艺条件下为定值;

- P:抛光垫对晶圆表面施加的下压力;

- v:晶圆与抛光垫之间的相对运动速度。

所以可以得到,如果我们要提升去除速率,可以通过提高抛光压力或提高相对旋转速度。

但通常,去除速率与工艺优化效果之间,存在 tradeoff 关系。而CMP 工艺需要就是在产能与抛光质量之间找到最优平衡。

对应第二张图,左上角红色文字明确了这部分的核心:These describe How uniform polished Or polish quality(这些指标用于描述抛光的均匀性与抛光质量)。

(2) 均匀性(Uniformity)

Uniformity of film removed or film remaining

- 均匀性越好,代表晶圆从中心到边缘的抛光厚度越一致,器件性能的波动越小;

- 若均匀性差,会出现晶圆中心过抛、边缘欠抛(或反之),导致部分区域器件结构受损、部分区域平坦化不达标,最终造成良率暴跌。

与非均匀性NU是对应关系:均匀性越高,NU 值越小。

(3) 选择比(Selectivity)

例如,铜互连 CMP 中,需要铜的去除速率远高于钽阻挡层的去除速率,当铜被抛完、露出阻挡层时,抛光速率会急剧下降,避免过抛损伤下层的低 k 介电层与器件结构。

(4) 台阶高度比(Step Height Ratio, SHR)

-

-

-

公式:

由于 CMP 会优先磨平凸起的高点,抛光后台阶高度必然降低,因此SHR 永远小于 1;

SHR 越小,代表平坦化效果越好。SHR 越接近 0,说明抛光后的表面越接近完美的全局平面,越能满足先进制程光刻的工艺要求。

7.2.4 抛光终止(Polish Termination)

-

定时抛光(Timed polish)

要求:必须有精准、长期稳定的抛光速率,以及极高的抛光均匀性;同时需要频繁监控工艺状态,避免速率波动导致的欠抛 / 过抛。

-

电机电流终点检测(Motor Current Endpoint)

抛光过程中,晶圆与抛光垫之间的摩擦阻力,会直接反映在抛光电机的工作电流上。当目标薄膜被完全去除、露出下层阻挡层,或晶圆表面被完全磨平时,摩擦系数会发生突变,电机电流也会出现特征性跳变,系统以此为信号触发抛光停止。

-

原位膜厚测量(In-Situ Film Measurement)

内置干涉仪通过抛光垫上的窗口,利用光学干涉原理,实时无损地测量晶圆表面剩余的薄膜厚度,当厚度达到目标值时,立即停止抛光。研磨液的散射、晶圆表面的图形结构,会对光学信号产生干扰,增加测量难度。

7.2.5 CMP 工艺核心影响因素

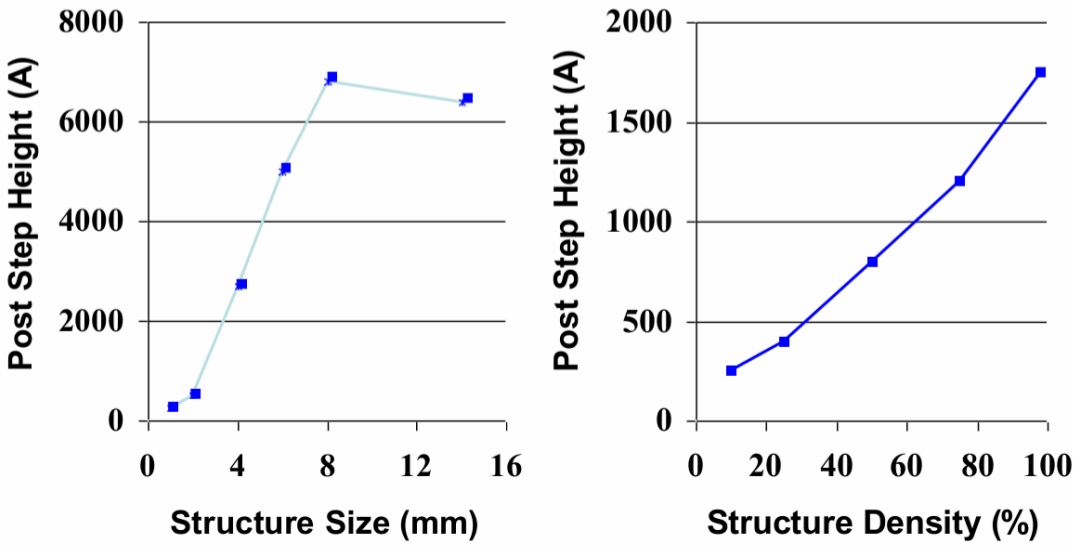

7.2.5.1 图形尺寸与密度的影响(Effect of Structure Size and Density on Post Step Height)

电路密度低的区域,抛光速率远高于高密度图形区域:低密度区域的凸起少,抛光压力更集中,去除速率更快;高密度区域的凸起多,压力被分散,去除速率更慢。

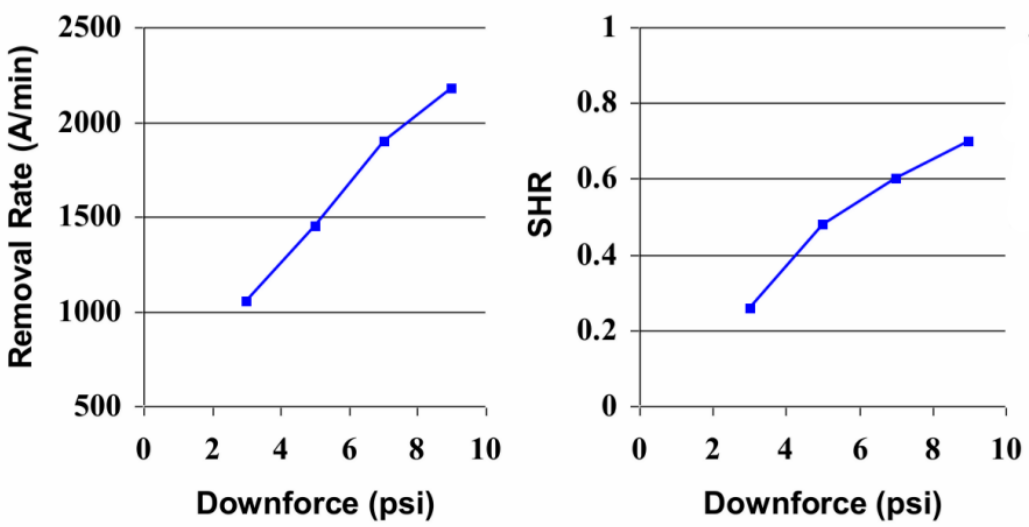

7.2.5.2 下压力的影响(Effect of Downforce on Removal Rate and Planarity)

-

下压力增大,抛光去除速率呈线性上升。

-

下压力增大,衬垫变形以及后续"谷区"局部压力的上升,台阶高度比 SHR 同步上升,从而导致平坦化效果显著劣化(SHR 越小,平坦化效果越好)。

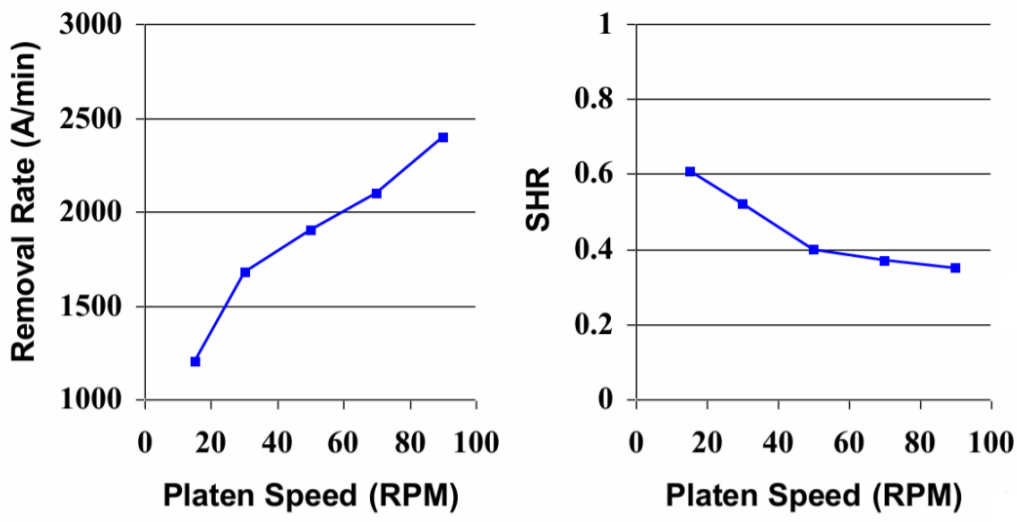

7.2.5.3 抛光平台转速的影响(Effect of Platen Speed on Removal Rate and Planarity)

- 抛光平台转速提升,去除速率呈线性上升。

- 平台转速提升,台阶高度比 SHR 持续下降,平坦化效果显著变好。

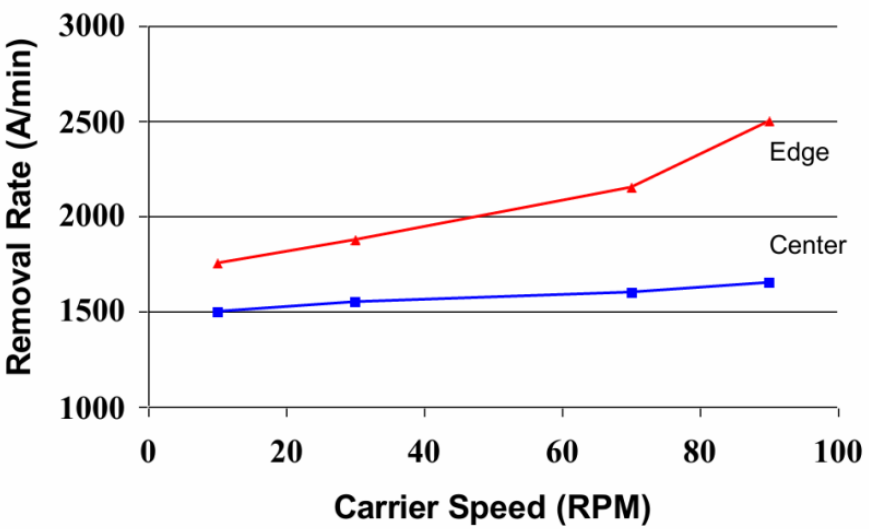

7.2.5.4 晶圆载具转速的影响(Effect of Carrier Speed on Wafer Center and Edge Removal Rates)

载具转速提升时,晶圆中心和边缘的去除速率均会上升,但边缘的去除速率上升幅度远大于中心,晶圆中心和边缘的速率差会持续扩大。

晶圆边缘的旋转半径远大于中心,角速度一致时,边缘的线速度远大于中心。

下面给出一个例子,一定要会判断:

| 变量 | 对去除速率(RR)的影响 | 对晶圆表面质量的影响 | 核心原理 |

|---|---|---|---|

| 下压力(Downforce) | ↑ | ↓ | 更高的压力会增强机械研磨作用,直接提升材料去除速率;但压力过大会造成晶圆划伤、碟形凹陷甚至碎裂,严重破坏表面平整度。 |

| 抛光垫转速(Pad speed) | ↑ | ↑ | 更高的相对转速会增大摩擦力与剪切力,提升去除速率;同时能改善抛光液分布,减少局部缺陷;但转速过高会引发热量堆积、抛光液供应不足,反而降低表面质量。 |

| 晶圆转速(Wafer speed) | ↑ | ↑ | 晶圆与抛光垫间的相对速度提升,会增强机械研磨作用,提升去除速率;均匀的接触运动可改善平面化效果,提升表面均匀性。 |

| 抛光液流量(Slurry flow rate) | ↑ | ↓ | 充足的流量可将新鲜磨粒与化学试剂输送到抛光界面,提升去除速率;流量过高会稀释反应试剂,过低则会导致磨屑堆积、划伤晶圆,均会降低表面质量。 |

| 抛光垫使用时长(Pad age) | ↓ | ↓ | 抛光垫磨损、表面玻璃化会降低磨粒保持能力与接触均匀性,导致去除速率持续下降;老化的抛光垫失去平面度,易造成抛光不均、引入缺陷,降低表面质量。 |

| 抛光液温度(Slurry temperature) | ↑ | ↓ | 温度升高会加速化学刻蚀反应,提升去除速率;但温度过高会导致过度化学腐蚀、材料选择性失效,同时引发热膨胀问题,破坏表面平整度。 |

Except rotation speed All faster makes worse.

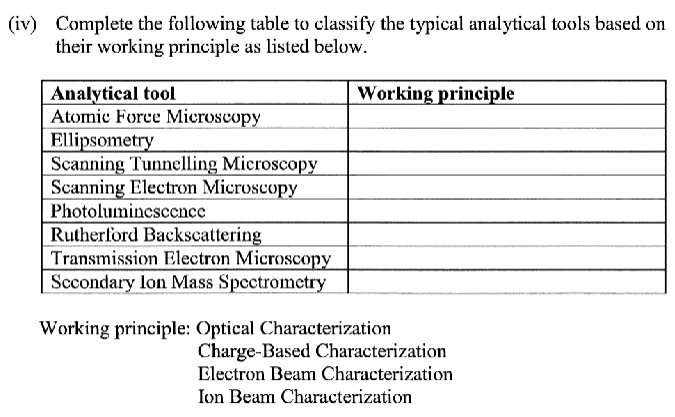

8 表征技术

半导体行业的表征技术主要分为四类:

- Optical Characterization(光学表征)

- Charge-Based Characterization(电荷基表征)

- Electron Beam Characterization(电子束表征)

- Ion Beam Characterization(离子束表征)

8.1 Optical Characterization(光学表征)

-

Optical Microscopy(光学显微镜)

-

Ellipsometry(椭圆偏振测量术)

-

Transmission(透射光谱技术)

-

Photoluminescence(光致发光)

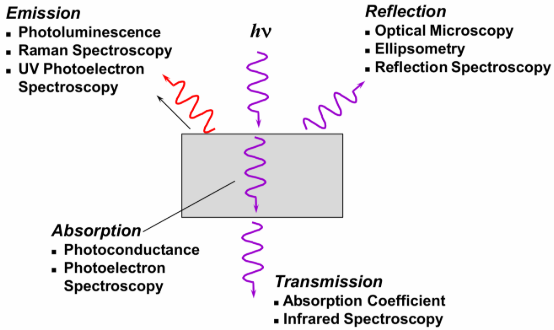

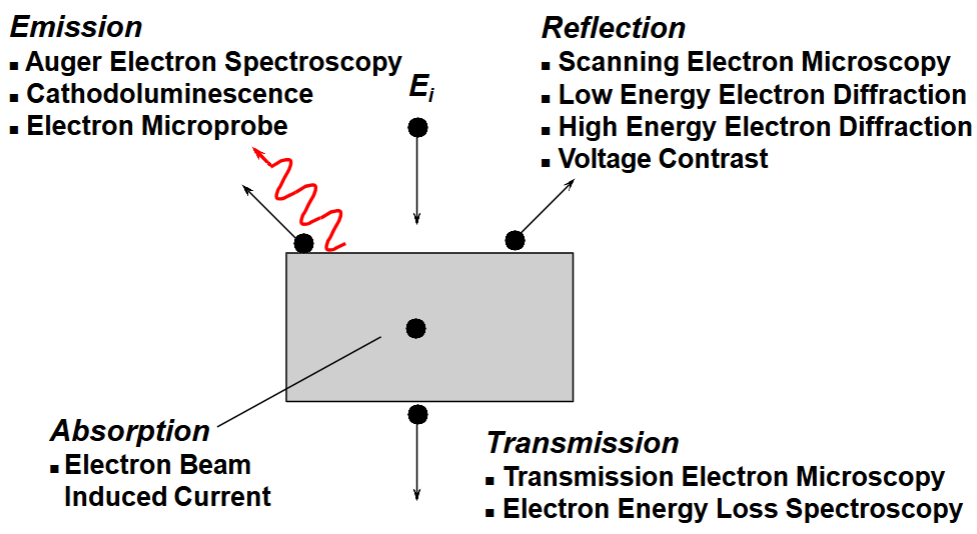

所有光学表征技术,本质都是基于入射光(能量为

| 相互作用类型 | 核心原理 | 对应表征技术 |

|---|---|---|

| 反射(Reflection) | 光入射到样品表面后发生反射,通过反射光的偏振、强度、相位变化提取信息 | 光学显微镜、椭偏仪、反射光谱 |

| 透射(Transmission) | 光穿过样品,通过透射光的强度、波长变化提取信息 | 吸收系数测量、红外光谱 |

| 吸收(Absorption) | 光被样品吸收,激发材料内的载流子,通过电学 / 光学响应提取信息 | 光电导测试、光电子能谱 |

| 发射(Emission) | 样品被入射光激发后,通过载流子复合发出特征光,通过发射光的光谱提取信息 | 光致发光、拉曼光谱、紫外光电子能谱 |

8.1.1 Optical Microscopy(光学显微镜)

单个孤立的物体,只要能反射足够的光,哪怕尺寸远小于分辨率极限,也能被检测到。但是两个相邻点能被清晰分辨的最小间距,存在物理极限,由光的衍射效应决定。

瑞利判据核心公式

各参数含义:

-

-

-

NA:数值孔径,由物镜的光学特性决定,

根据公式可得光学衍射极限:

例如,可见光波长

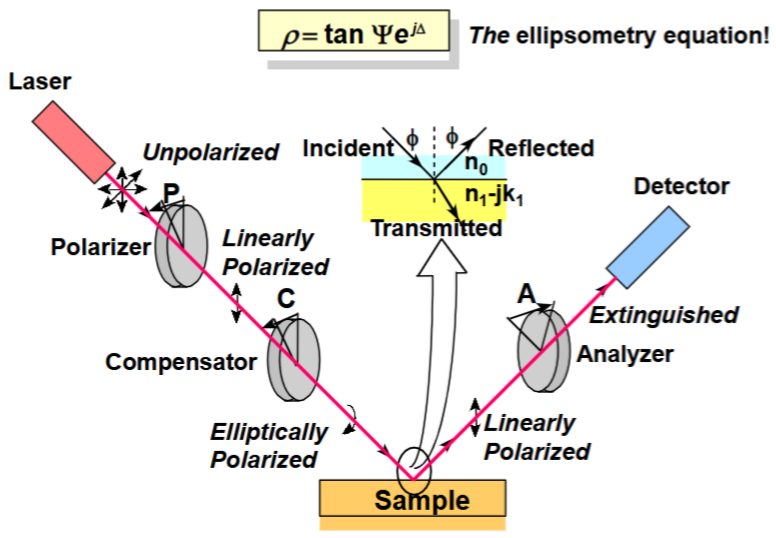

8.1.2 Ellipsometry(椭偏仪)

椭偏仪的核心是利用偏振光的反射特性,提取薄膜的厚度与光学参数:

-

光路流程

激光器发出非偏振光

-

公式

其中

Ellipsometry的特点:

- Nondestructive technique

- Film thickness measurement; can measure film thicknesses down to 1 nm

- Refractive index determination; can measure refractive index of thin films of unknown thickness

- Azimuth angles can be measured with great accuracy

- Measures a ratio of two values

- Highly accurate and reproducible (even in Tow light levels)

- No reference sample necessary

- Not as susceptible to scatter, lamp or purge fluctuations.

- Surface uniformity assessment

- Composition determinations

- Can be used for in situ analysis

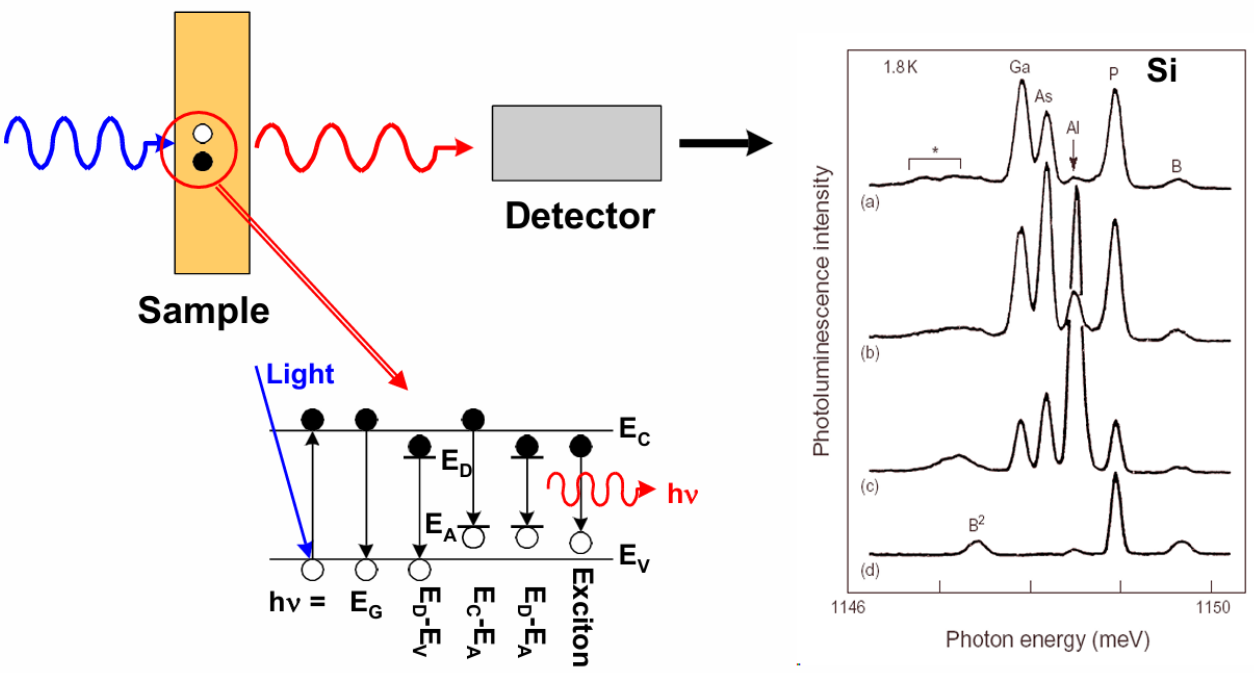

8.1.3 光致发光(Photoluminescence, PL)

- 入射激光的能量大于半导体的禁带宽度Eg,照射样品时,会将价带的电子激发到导带,形成电子-空穴对(ehp);

- 激发态的电子与空穴发生复合时,会以光子的形式释放能量,发出特征光(emit light),即光致发光。

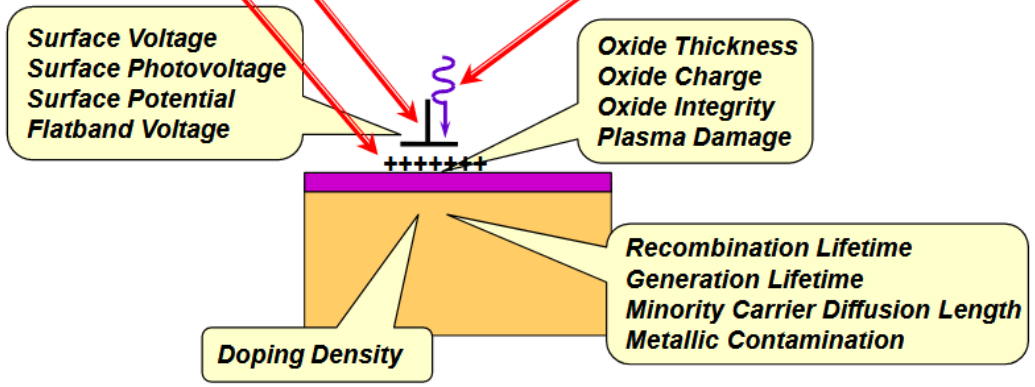

8.2 Charge-Based Characterization(电荷基表征)

电荷以化学方式或通过电晕电荷(流体的电离)沉积在晶片上测量;

非接触式表面电压/表面光电压;

可以通过光增强测量。

- Scanning Tunnelling Microscopy

- Atomic Force Microscopy

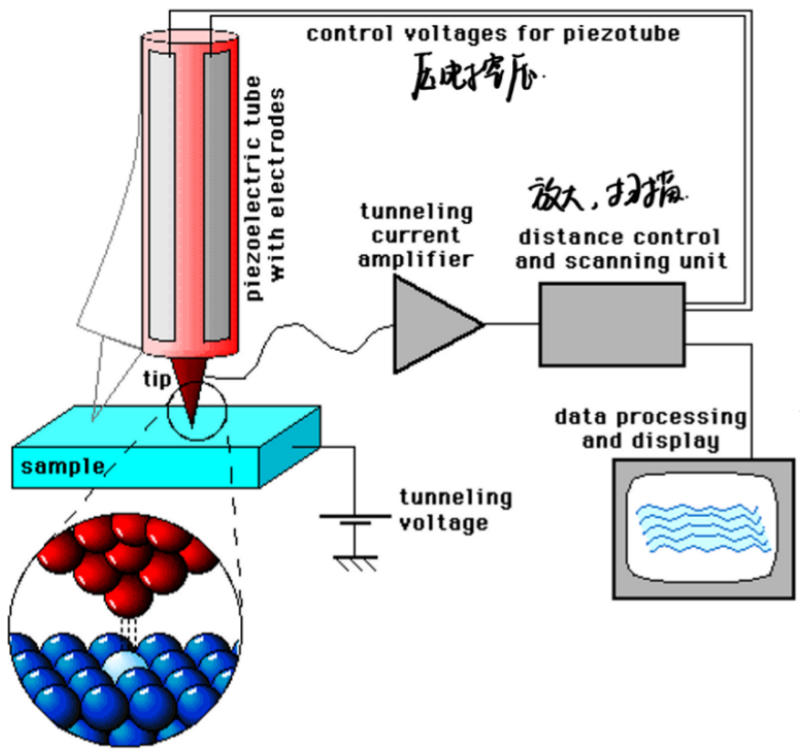

8.2.1 Scanning Tunnelling Microscopy(扫描隧道显微镜)

用于对表面进行 atomic level 成像

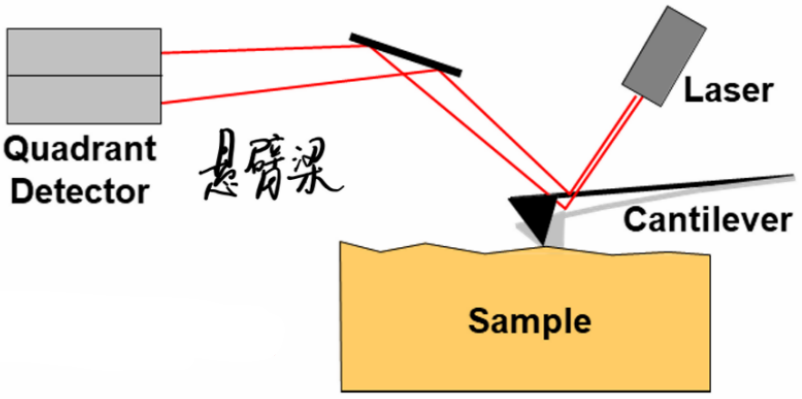

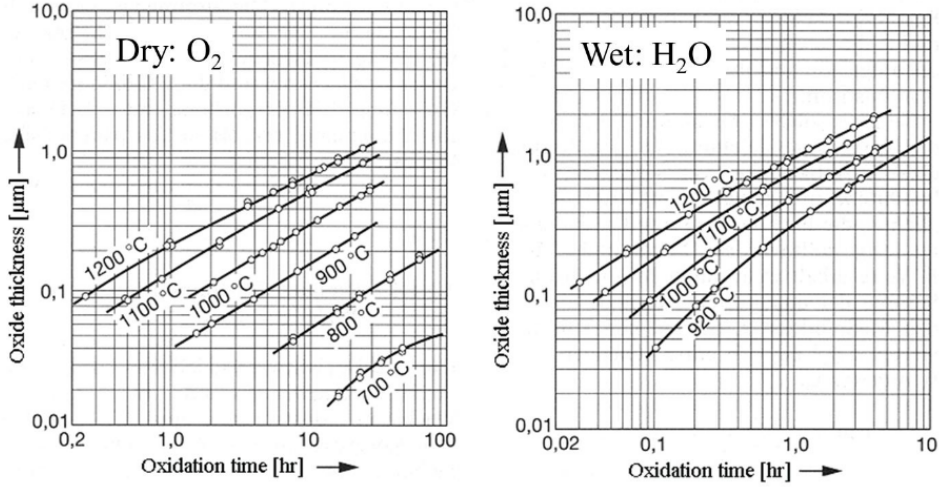

8.2.2 Atomic Force Microscopy(原子力显微镜)

要会画图以及解释工作原理:

AFM的工作原理:

A sharp tip is scanned over a surface with feedback

Piezo-electric scanners maintain the tip at two stage:

- Constant force: Height information

- Constant height: Force information

Tips(探针) are typically made from

Feedback from the photodiode difference signal enables the tip to maintain either a constant force or constant height.

有三种工作模式:

- Contact mode(High resolution)

- 针尖以与表面紧密接触的方式扫描样品

- 针尖上的排斥力约为 10-8 N

- 该力通过使用压电元件将样品压向悬臂梁来设定

- 压电电压与样品高度成正比

- Non-contact mode(Low resolution)

- 针尖位于样品表面上方 5‐15 纳米处。通过检测针尖与样品之间作用的范德华吸引力, 并在表面上方扫描针尖, 从而构建出形貌图像。

- Tapping mode

- 悬臂梁以其共振频率 ( 50‐500 kHz ) 振荡

- 当探针未与表面接触时, 悬臂以高振幅 (约 20 纳米) 振荡然后, 振荡的探针向表面移动, 直到开始轻微接触或轻敲表面

- 振荡幅度减小,振荡幅度的减小用于测量表面特征

要会权衡快慢和分辨率高低,和模式对应。

8.3 Electron Beam Characterization(电子束表征)

主要记住下面三个即可:

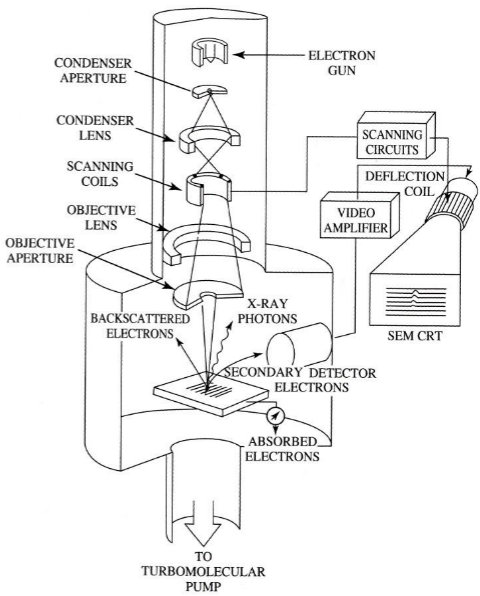

- Scanning Electron Microscopy(二次电子反射)

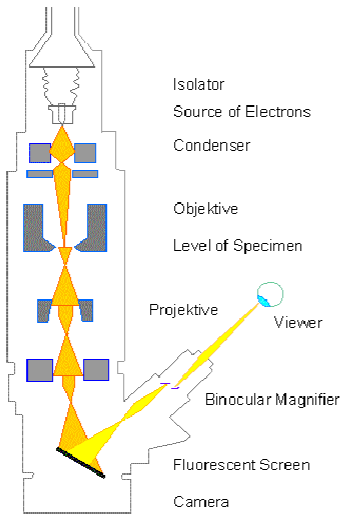

- Transmission Electron Microscopy

- Electron Microprobe

8.3.1 电子束和固体材料相互作用

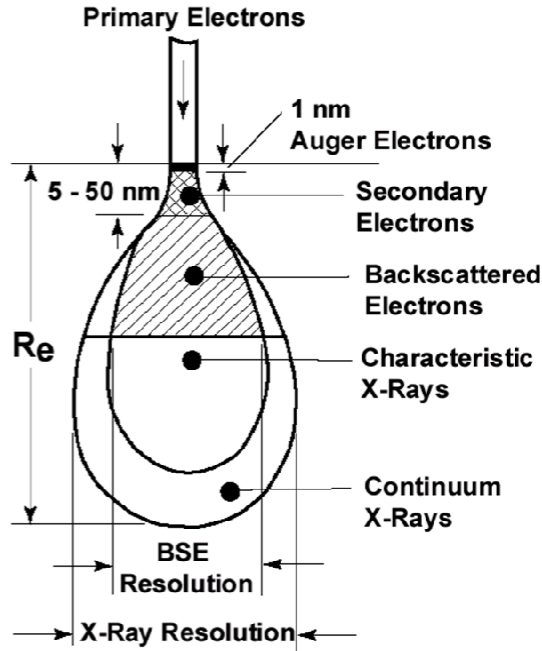

入射电子会被加速到 1-30 keV,这是 SEM 最常用的加速电压范围。

加速电压越高,电子动能越大,穿透样品的深度越深。

电子束的扩散效应:电子束入射固体后,会和样品原子发生弹性/非弹性散射,束斑会像水滴落地一样扩散开,形成一个梨形的相互作用体积,电子能穿透的最大深度被称为电子射程

电子射程是电子束能穿透样品的最大深度:

加速电压越高、材料密度越小,电子穿透得越深。

硅材料密度固定为 2.33g/cm³,代入通用公式得到简化式:

典型示例:当加速电压

8.3.2 Scanning Electron Microscopy(SEM)

原理:The electrons interact with atoms in the sample, producing various signals that contain information about the sample’s surface topography and composition.

中文对照:高能聚焦电子束扫描样品表面时,会与样品中的原子发生相互作用,产生多种携带样品信息的信号,这些信号可用于解析样品的表面形貌与化学成分。

中间腔体是中空的。

-

半导体量产常规检测

- 线宽测量(Line width)

- 形貌表征(Topology)

-

阴极荧光(Cathodoluminescence, CL)

- 特征光发射(Light emission)

-

电子微探针(Electron microprobe)

- X 射线发射(X-ray emission)

8.3.3 Transmission Electron Microscopy

TEM 和 SEM 的核心本质区别是:SEM 收集样品表面反射或散射的电子,观测表面形貌;TEM 收集穿透样品的透射电子,观测样品内部的截面晶体结构。

-

入射电子会被加速到 100-300keV

-

样品必须被减薄到纳米级超薄厚度

Example:

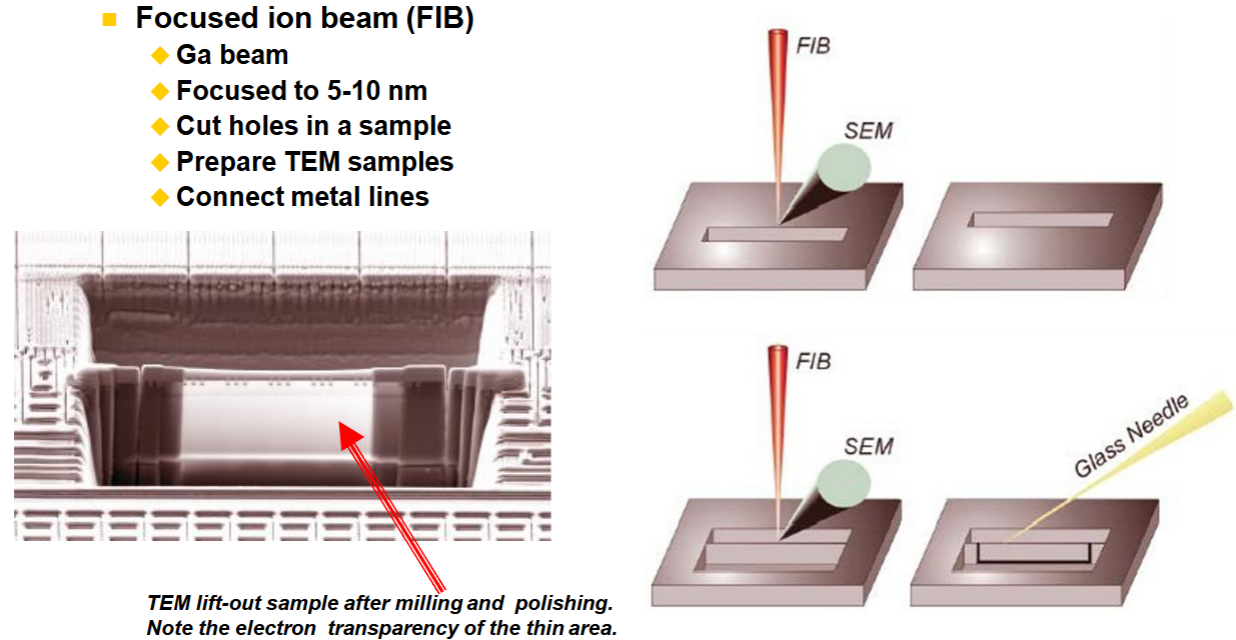

FIB 的原理是:将高能镓离子(

8.3.4 Electron Microprobe(EMP)

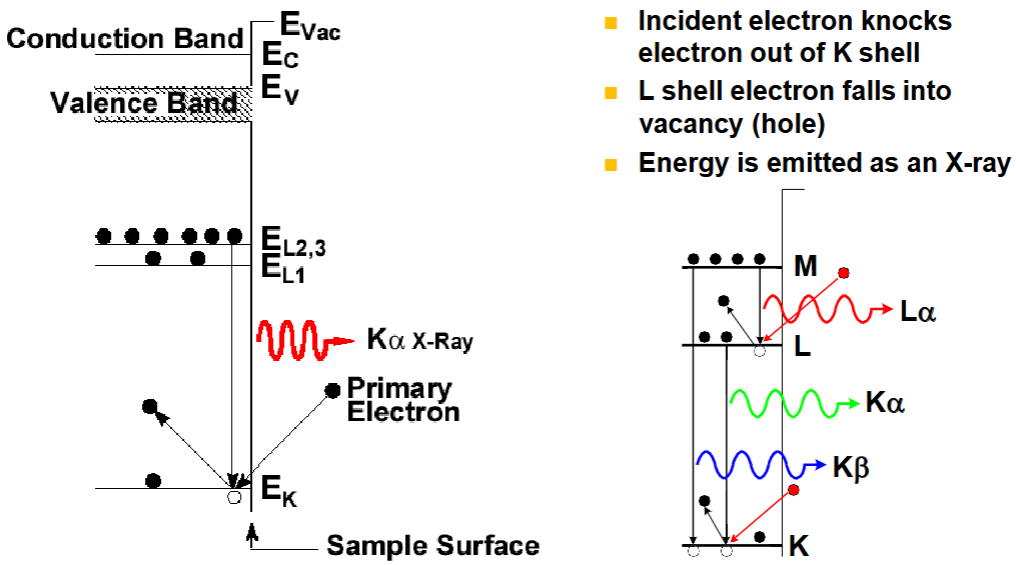

- 内层空穴形成:高能入射电子将原子内层 K 壳层的束缚电子打出,在内层形成一个空穴,原子进入不稳定的激发态;

- 外层电子跃迁:外层(L/M 壳层)的电子会自发向低能级的内层空穴跃迁,填补空穴,让原子回到稳定的基态;

- 特征 X 射线发射:电子跃迁过程中,会释放出等于两个能级能量差的能量,这份能量以特征 X 射线的形式发射出来。

核心优势:

- Nondestructive technique (无损检测)

- trace impurities and major components in a single analysis (一次分析可同时完成样品中主量元素、微量元素、痕量杂质的同步检测

- Two-dimensional information by scanned beam (二维元素分布成像)

另外需要记住这种方式的轻元素检测能力弱:对原子序数 Z<10 的轻元素(H、Li、Be、B、C、N、O、F 等)检测灵敏度极差。

8.4 Ion Beam Characterization(离子束表征)

- Secondary Ion Mass Spectrometry

- Rutherford Backscattering

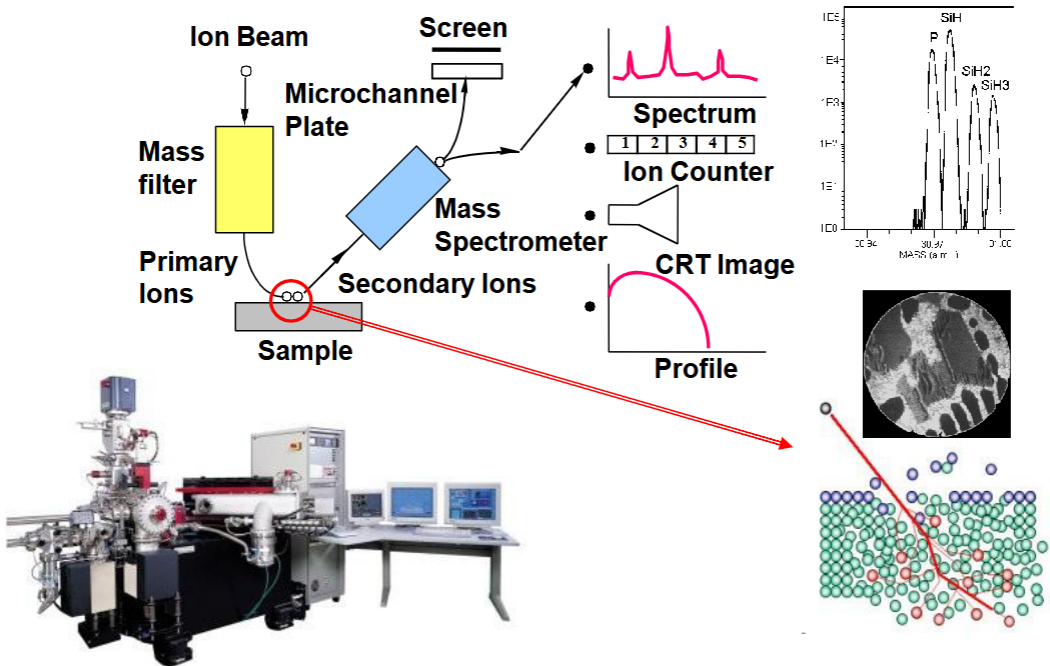

8.4.1 Secondary Ion Mass Spectrometry

如图所示,SIMS 的流程分为四步:

-

一次离子束生成与聚焦

-

二次离子溅射产生

-

质谱分离与元素识别

-

信号检测与结果输出

SIMS 是最常用的掺杂分布分析方法。其原理就是从样品中溅射产生原子,然后对溅射出来的离子质量进行分析:

- 离子质量

- 离子强度

优点:

- 可获得深度分布信息;

- 能够分析所有元素;

- 是所有分析技术中灵敏度最高的;

- 可同时检测多种杂质

局限性:

- 属于破坏性检测方法;

- 易受基体效应影响:

- 离子产额会随表面成分变化而改变;

- 需要标准样品进行浓度测定,需独立进行深度测量

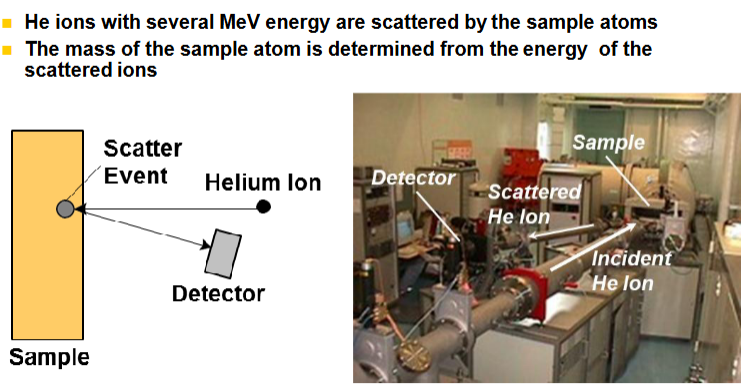

8.4.2 Rutherford Backscattering

RBS 的物理基础是卢瑟福弹性散射,核心是通过高能氦离子与样品原子的碰撞,实现元素的定性、定量与深度分布分析。

- 碰撞后 He 离子的能量损失,和被碰撞的样品原子的质量直接相关:原子越重,碰撞后背散射 He 离子的能量越高,以此实现元素种类的定性识别;

- 碰撞发生的深度越深,He 离子在入射和出射路径上的能量损失越多,以此实现元素深度分布的表征。

| 表征介质 | 表征工具 | 工作原理 |

|---|---|---|

| 光学表征 | 光学显微镜 | 反射 |

| 椭圆偏振法 | 反射 | |

| 吸收系数 | 透射 | |

| 光致发光 (PL) | 发射 | |

| 红外光谱 (IR) | 透射 | |

| 电子表征 | 扫描电子显微镜 (SEM) | 反射 |

| 透射电子显微镜 (TEM) | 透射 | |

| 电子探针 | 发射 | |

| 离子表征 | 二次离子质谱 (SIMS) | 反射 |

| 卢瑟福背散射 (RBS) | 反射 |

下面给出两道例题

Example 1:

Example 2:

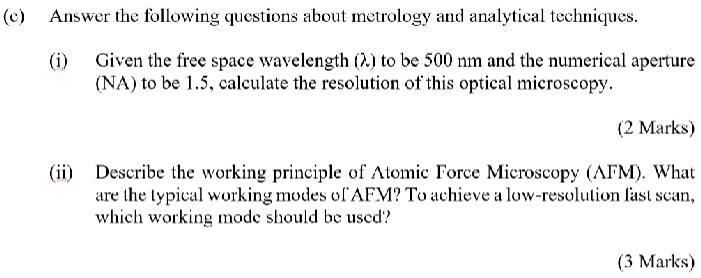

9 Dielectrics

为什么选择二氧化硅作为最重要的钝化材料?(可以选择性的背2-3条即可)

-

Passivate (protect) high field regions on semiconductor surface

-

Masking for selective ion implantation

-

Very good etching selectivity

-

As an insulating layer in the gate region of a MOS transistor

-

Stable and reproducible Si/SiO2 interface, final circuit protection, etc

-

Easily to form by thermal oxidation

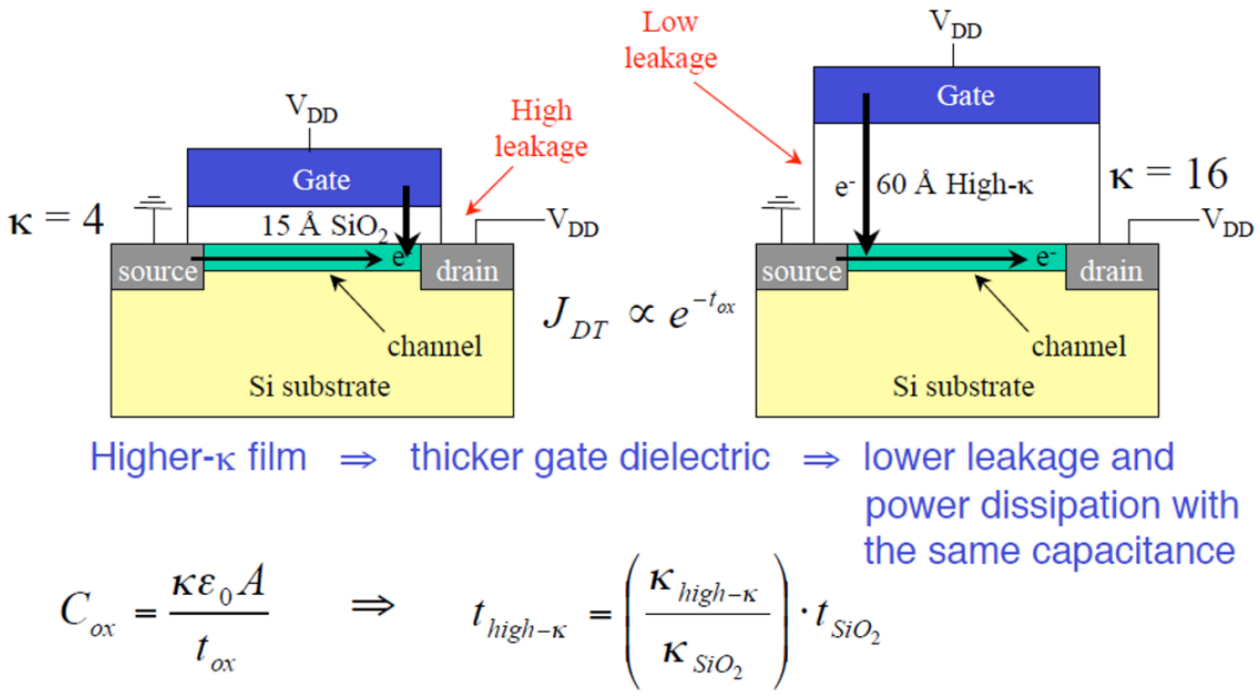

根据 MOSFET 的等比例缩小定律,晶体管的栅长、尺寸缩小时,栅氧层厚度必须同步缩小,才能保证栅极对沟道的强控制能力,抑制短沟道效应。但当

-

栅极漏电流(Leakage current):导致芯片静态功耗飙升,甚至电路工作不稳定、逻辑翻转失效,是

-

Performance degradation due to

- Carrier quantization in the channel and depletion in poly-Si gate

-

Degradation and breakdown

-

Dopant penetration through gate oxide

-

Atomic level Defects

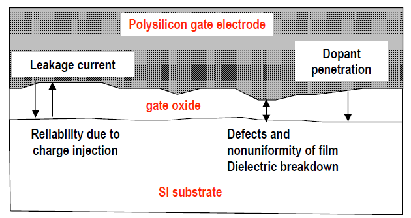

9.1 Thermal Oxidation(热氧化)

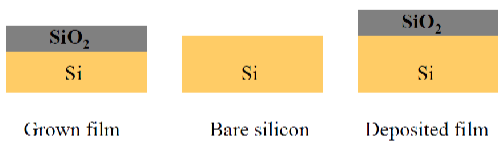

热氧化是在 900-1200℃的高温环境下,让氧化剂(氧气

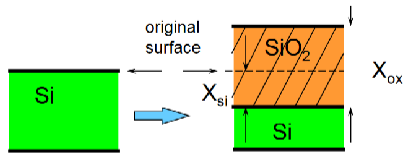

氧化反应并非在

- 硅衬底消耗:氧化反应发生在

- 2.2 倍体积膨胀:生成的

| 氧化方式 | 化学反应式 | 核心特性 |

|---|---|---|

| 干氧氧化(Dry Oxidation) |

|

O₂在 SiO₂中扩散速率慢,氧化生长速率低;但生成的 SiO₂致密度高、缺陷少、界面态低、击穿场强高 |

| 湿氧氧化(Wet Oxidation) |

|

|

相比较dry氧化,wet氧化更快反应,但是表面质量差。

9.1.1 硅衬底消耗厚度(平面氧化)

这张图给出了氧化层厚度与被消耗硅厚度的定量关系,被消耗的硅厚度

其中:

-

-

代入数值可得到常用简化式:

也就是说生长 1μm 的 SiO₂,会消耗 0.46μm 的硅。

9.1.2 热氧化动力学模型:Deal-Grove 模型

Deal-Grove 模型可以预测氧化层厚度与氧化时间、温度关系:

其中:

-

-

- A、B:氧化速率系数,由氧化温度、氧化剂类型、硅晶向决定;

-

通过公式变形,可直接得到氧化层厚度的显式解,这个公式考试会给,但是要知道各个参数是什么意义:

根据氧化层厚度的不同,可以分为两种情况:

-

薄氧化层(线性区)

当氧化层极薄时,

- 氧化层厚度与氧化时间呈线性关系,氧化速率由界面反应速率决定。

- 速率系数:

-

厚氧化层(抛物线区)

当**氧化层很厚*时,

- 氧化层厚度与氧化时间的平方根呈抛物线关系,氧化速率由氧化剂在 SiO₂中的扩散速率决定。

- 速率系数:

9.1.3 氧化物生长(Oxide Growth)

-

初始生长阶段:

-

氧化物形成动力学(Deal-Grove 模型)非常适用于湿式氧化,有水蒸气的情况下,氧化速率会更快。一方面水分子更小更容易传过氧化层与基底接触进行反应,另一方面羟基(

-

对于干式氧化,在生长的前 300A 内会发生极快的氧化。原因是孔隙的存在,空间电荷区的形成(氧离子和空穴之间)。

-

-

氧化速率的取向依赖性:

- 生长速率取决于 Si 原子的表面密度。

- Si(111) 表面原子密度 > Si(110) 表面原子密度 > Si(100) 表面原子密度。

- Si(111) 表面氧化物的生长速率 > Si(110) 表面氧化物的生长速率 > Si(100) 表面氧化物的生长速率。

- 生长速率取决于线性速率常数。抛物线生长速率(与扩散率相关)与晶体取向无关。

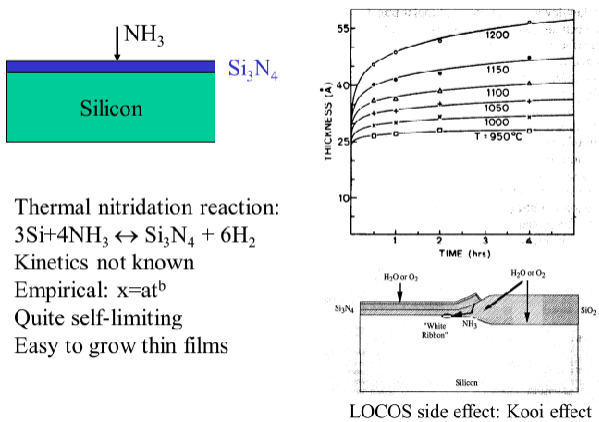

9.2 Thermal Nitridation(热氮化)

氨气扩散很差,自动停在1nm以内厚度,比sio2更硬,可以做抛光停止层。

| 热生长 | CVD |

|---|---|

| 氧气来自气相(gas phase),硅来自基底 | 氧气和硅都来自气相 |

| 二氧化硅层会生长进入硅层 | 在硅层的表面 |

| 高质量 | 低温度和高生长率(High growth rate) |

9.3 Chemical Vapor Deposition(CVD)

9.3.1 沉积流程

整个过程分为气相输运、表面反应、副产物排出三个阶段,完整流程如下:

- 气态/蒸汽态前驱体被通入反应腔室;

- 前驱体分子穿过腔室内的边界层,到达晶圆衬底表面;

- 前驱体分子吸附在衬底表面;

- 吸附的前驱体分子在衬底表面发生迁移;

- 前驱体在衬底表面发生化学反应,生成固态产物;

- 固态反应产物在衬底表面形成晶核;

- 晶核长大为孤立的岛状结构;

- 岛状结构相互合并,最终形成连续的固态薄膜;

- 反应产生的气态副产物从衬底表面脱附;

- 气态副产物穿过边界层,扩散到主气流中;

- 气态副产物随主气流排出反应腔室。

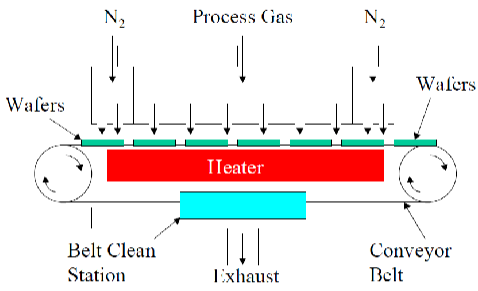

9.3.1.1 常压化学气相沉积(Atmospheric Pressure CVD, APCVD)

采用传送带式连续反应系统:晶圆平铺在传送带上,底部加热器提供反应温度,工艺气体从顶部均匀喷淋到晶圆表面,氮气作为隔离气防止前驱体提前反应,同时配套原位传送带清洁站与排气系统。

常压下气体反应活性高,沉积速率极快,适合厚膜生长。

9.3.1.2 低压化学气相沉积(Low Pressure CVD, LPCVD)

在低真空环境(

- 优势:低压下气体分子平均自由程大幅增加,前驱体在晶圆表面的扩散更均匀,因此薄膜台阶覆盖性、片内 / 片间均匀性极佳;晶圆垂直装载,单批次可处理 200 片晶圆,产能极高,颗粒污染少。

- 劣势:工艺温度高(通常 600~900℃),无法用于金属互连后等对温度敏感的工艺,高温会限制个别低熔点材料使用。

9.3.1.3 等离子体增强化学气相沉积(Plasma Enhanced CVD, PECVD)

通过射频(RF)功率激发产生等离子体,利用等离子体中的高能电子为前驱体提供反应活化能,在低温下实现薄膜沉积的 CVD 工艺。

采用平行板电容耦合等离子体腔室:晶圆放置在带加热功能的衬底台上,顶部电极接 RF 功率,通入的工艺气体被 RF 激发产生等离子体,反应副产物由真空泵抽出。

10 MOS Gate Dielectric

10.1 介质的本征击穿

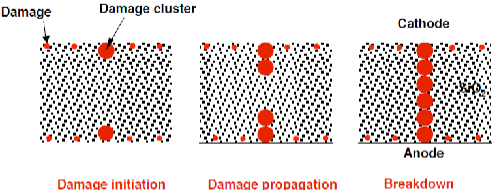

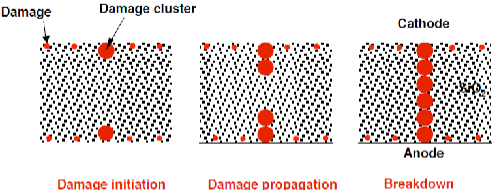

击穿是一个"损伤萌生-扩展-贯穿失效"的渐进式过程:

-

损伤萌生(Damage initiation)

损伤始于阳极与阴极界面,直接导致介质的漏电流上升、绝缘性能退化。

-

损伤扩展(Damage propagation)

随着电场持续施加,界面处的损伤点不断累积变大,沿着电场方向(阴极到阳极)形成连续的损伤团簇链,缺陷不断向介质本体内部扩展,介质的绝缘性能持续劣化,漏电流呈指数级上升。

-

击穿(Breakdown)

当损伤团簇最终形成贯穿整个介质层的导电通路时,阴极与阳极直接导通,介质彻底失去绝缘能力,发生永久性的硬击穿,MOSFET 器件直接短路失效。

10.2 High-k Dielectrics

为什么需要 High-k 介质?

根据 MOSFET 饱和漏电流公式:

其中:

-

-

-

随着晶体管尺寸等比例缩小:

- 宽长比

- 要维持器件驱动能力

To keep drain current constant:

-

-

10.2.1 高 k 栅介质的优势

| 结构 | 传统 SiO₂栅氧 | 高 k 栅介质 |

|---|---|---|

| 介电常数 k | 4 | 16 |

| 物理厚度 | 15Å(1.5nm) | 60Å(6nm) |

| 栅电容Cox | 完全相同 | 完全相同 |

| 栅漏电流 | 极高 | 指数级降低 |

根据栅电容的公式:

要保持栅控能力(Cox)不变,高 k 材料的 k 值是

隧穿漏电流与介质厚度呈指数负相关(

要能写出一些 High-k材料的名称

-

不稳定 High-k 氧化物:

-

稳定 High- k 氧化物:

10.3 Low-k Dielectrics

低 k 材料的核心矛盾是:介电常数越低,材料的热机械性能越差,几乎所有热机械性能都比

Low-k 材料与 Cu 做互联,RC延迟低。

要记住几个 Low-k 材料的名字:

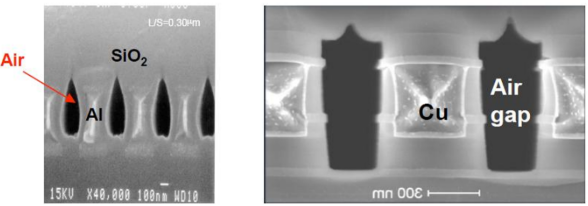

另外还需要了解 Air-gap as Low-k Dielectrics

空气的相对介电常数 k=1,这种方法就是在金属互连线之间制造封闭的空气间隙,用空气替代固体介质作为互连线之间的绝缘材料,将互连电容降到理论最低值。

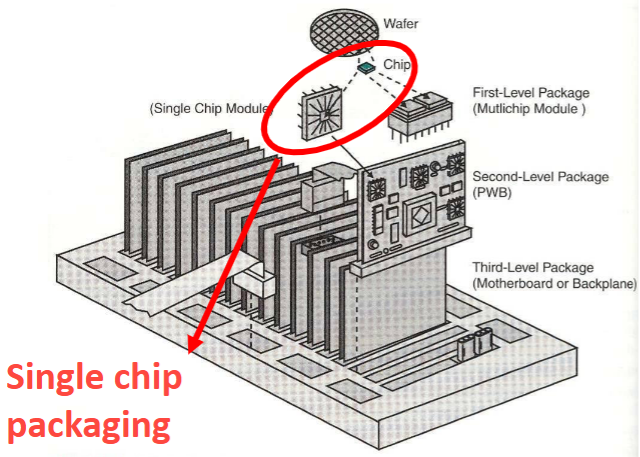

11 Packaging

封装是芯片制造(IC/MEMS 等)与最终产品之间的桥梁,是芯片实现功能、保障可靠性的核心载体。

11.1 单芯片封装(Single chip packaging, SCP)

整体功能:

- 确保设备在设计使用寿命内稳定可靠地实现其预设功能

半导体封装载体(SCP)的六大独立功能:

- Signal transmission and power to and from the chip (IC)

- Signal transmission and power to and from the next packaging level (PCB)

- Attachment to the next packaging level (PCB)

- Heat dissipation

- Protection of chip (mechanical and chemical)

- Space transformer: Fine-pitch IC vs. coarse-pitch PCB

11.2 互连技术

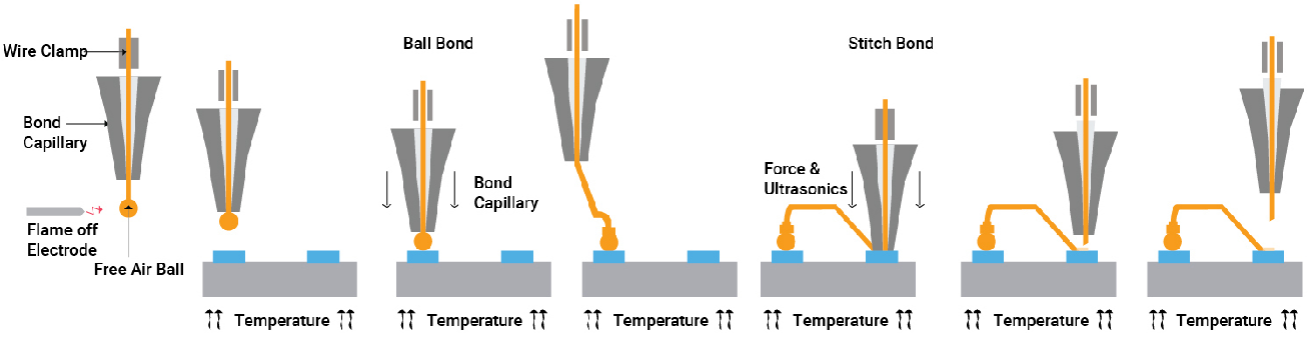

11.2.1 Wire Bonding(引线键合)

Welded to the pad by applied:

- Pressure

- Temperature

- Ultrasonic energy

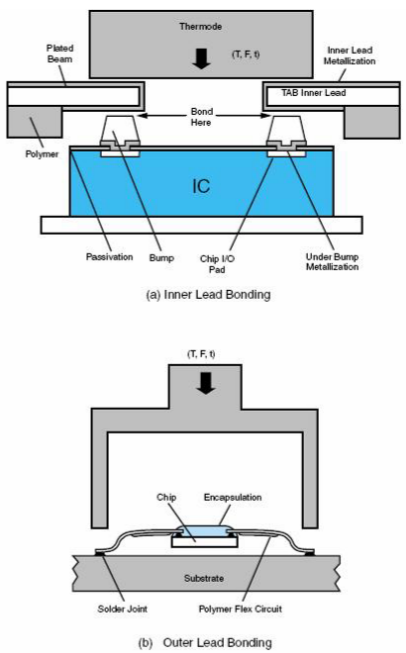

11.2.2 Tape Automated Bonding(载带自动键合)

-

Interconnection by metallized flexible polymer tape

-

All connections for a chip on one tape

-

Connection made in two steps:

- Inner Lead Bonding

- Connecting tape to chip

- Outer Lead Bonding

- Connecting tape to substrate

- Inner Lead Bonding

-

Connection made by thermocompression

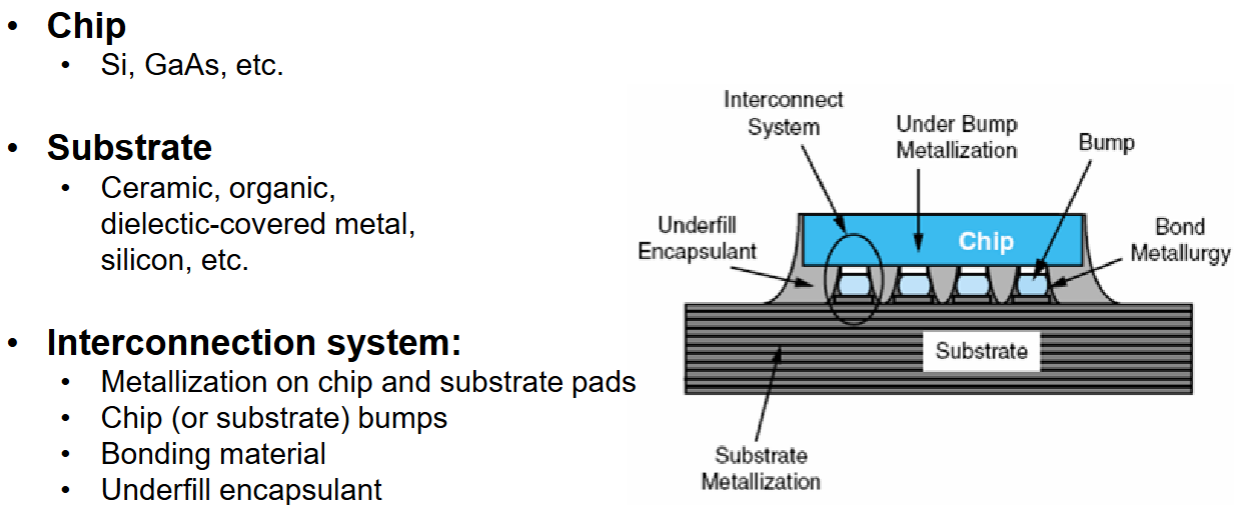

11.2.3 Flip chip(倒装芯片)

芯片有源面朝下,通过面阵列凸点直接与基板互连,所有连接同步完成。

11.2 多芯片封装(Single chip packaging, SCP)

将多颗裸芯片封装在同一个壳体内,实现系统/子系统功能。例如,将传感器芯片和 ASIC 处理芯片,传感器信号由 ASIC 直接调理,减少外部电路。其中关于面积的判定公式如下:

其中,

多芯片的封装效率提高了 50%,属于高密度集成封装。

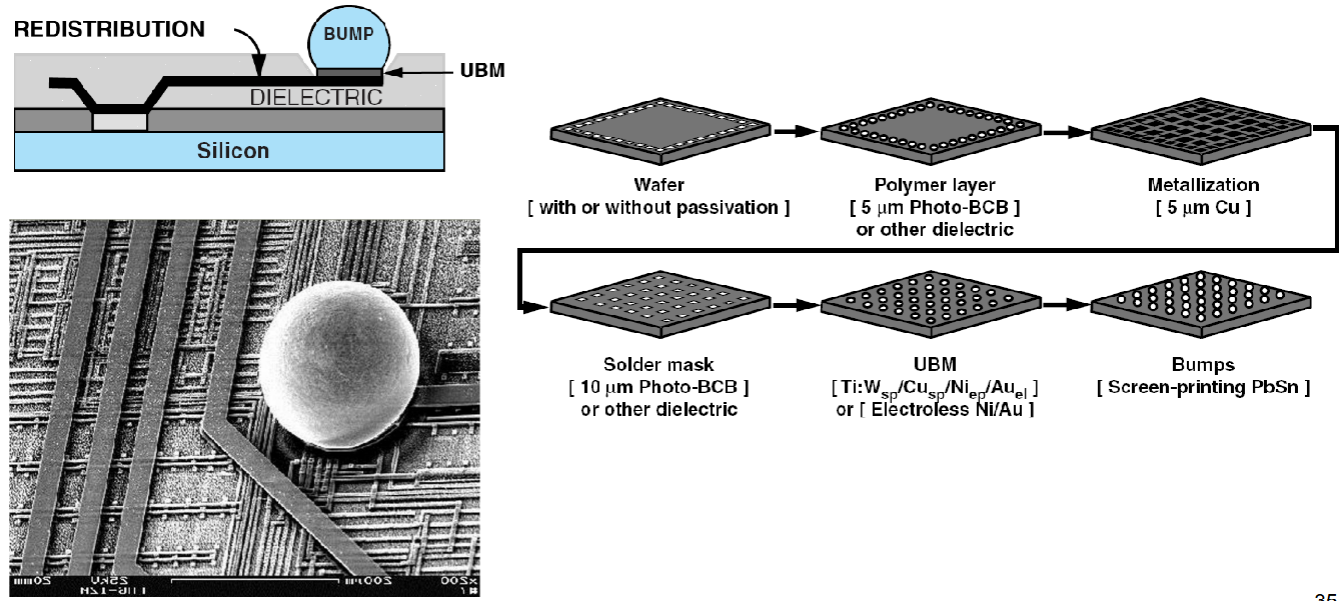

11.3 Wafer Level Packaging(晶圆级封装)

WLP是先在整片晶圆上并行完成封装

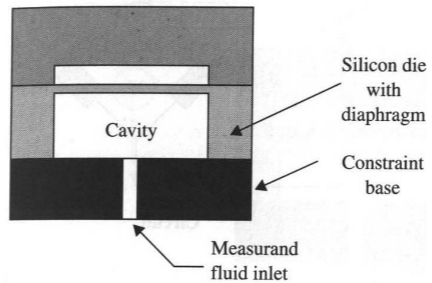

11.3.1 腔体密封工艺

Lid sealing:

-

To make a cavity

-

To protect fragile parts

-

Hermetic sealing

11.3.2 重布线层(RDL)

将芯片原始超细焊盘,重新布线转换成适配 PCB 装配的粗间距凸点

11.4 3D 封装

利用 Z 轴垂直方向堆叠,提升封装密度。主要有两种堆叠方式:

- 芯片堆叠(chip stacking):多颗芯片垂直叠放

- 封装堆叠(Package stacking):多个封装垂直叠放

互连方式的方式采用了引线键合、倒装芯片。

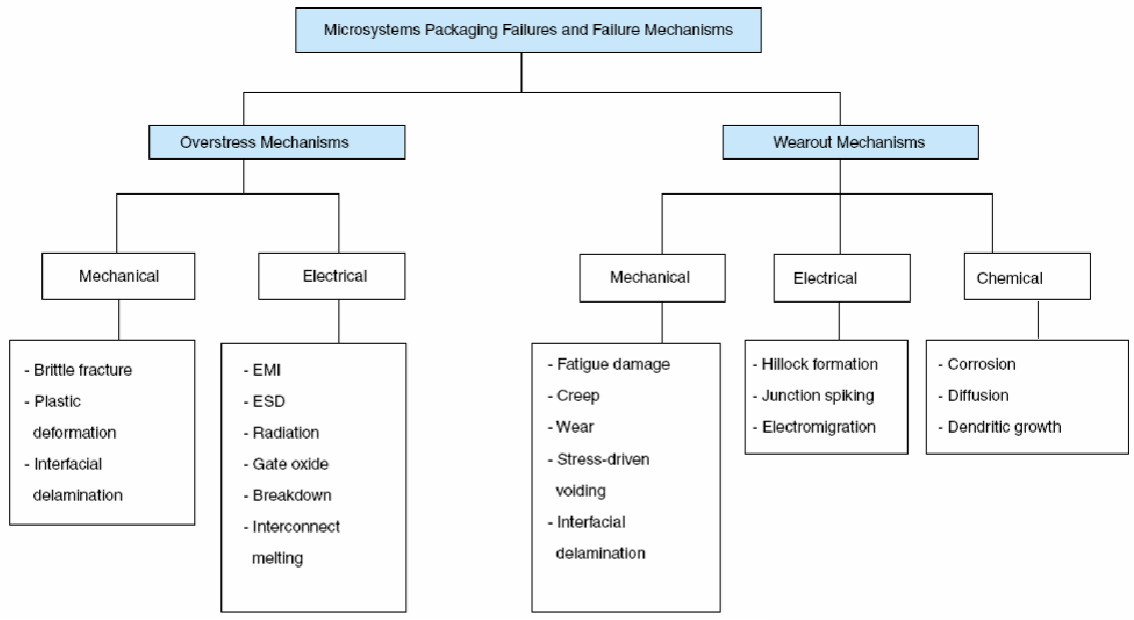

11.5 封装失效

下面图不用记,稍微了解即可:

11.5.1 热致失效(Thermally-induced failures)

所有失效几乎都被高温加速,最核心的诱因是不同材料的热膨胀系数(CTE)不匹配,温度变化时产生热机械应力,反复应力导致疲劳断裂。

Fatigue fracture(热疲劳断裂)就是温度反复循环导致:

- 环境温度变化(户外产品)

- 芯片开关机(通电发热→断电冷却)

- 反复热应力→焊料疲劳开裂

因此需要对抗热疲劳,主要有以下方式:

- Join materials with similar CTE

- Minimize distance from neutral point

- Minimize temperature variation

- Minimize temperature gradients

- Underfill for flip chips and BGAs

11.5.2 机械失效(Mechanical failures)

-

Brittle fracture(脆性断裂)

-

Brittle fracture的定义就是过应力失效,应力超过材料断裂强度。(Overstress failure, Stress exceeds fracture strength)

-

Designing against brittle fracture

- Design with margin to fracture strength of chosen material

- Stress considered includes stress induced by processing (also thermomechanical)

- Polish brittle materials (remove scratches: no sources for fracture propagation)

-

-

Delamination(分层)

-

定义:不同材料结合界面发生剥离。(Debonding of materials bonded together)

-

Design against delamination

- Process control

- Optimize adhesion

- Avoid sharp corners in package

-

11.5.3 电致失效(Electrically-induced failures)

不同电势物体电荷转移(如摩擦、人体接触)都会导致电致失效

电迁移这个概念要知道:金属原子在高密度电流驱动下,沿电流方向定向移动。其危害主要有两点:

- 金属线产生空洞

- 金属间产生枝晶

Design against electromigration:

- Decrease current density

- Aluminium and silver is susceptible of electromigration

- Copper is more resistant

11.5.4 化学失效(Chemically-induced failures)

Types of chemically-induced failures:

-

Electrochemical reactions

-

Diffusion

-

Dendritic growth

Increased reaction by

- Increasing temperature

- Increasing voltage

- Increasing stress

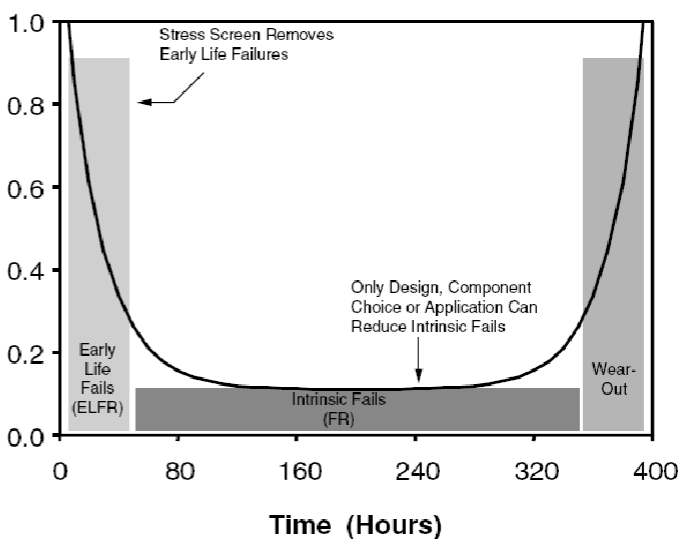

11.5.5 Failure rate

早期失效阶段:制造缺陷

正常使用寿命阶段:低故障率

耗损失效阶段:磨损老化