1 晶体管缩小时各参数变化

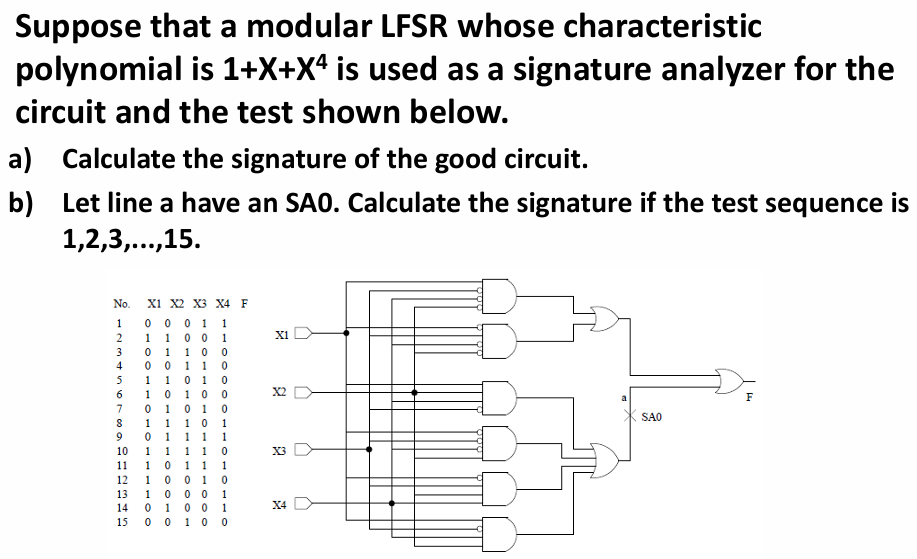

1.1 在恒定电场下

为了减弱短沟道效应带来的影响,各参数变化如下:

可以发现,当晶体管的宽长比等尺寸缩小

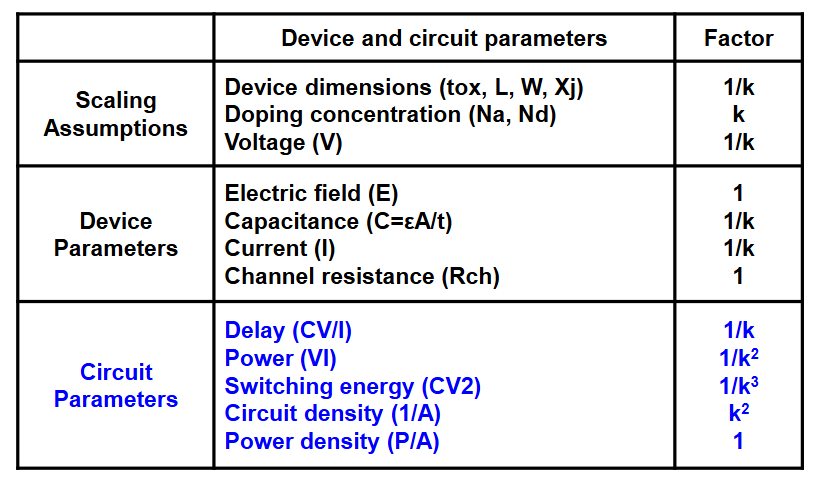

1.2 在恒定电压下

为了达到更高的时钟频率,缩小尺寸后各参数变化如下:

2 数据编码(Data Coding)

在本门课中,数据编码重点讲述了错误检测编码、错误纠正编码;错误检测编码主要包括奇偶校验码(Parity Checking)、循环冗余校验码(CRC)和定重码(m-out-of-n code);错误纠正编码主要是汉明码(Hamming Codes)。

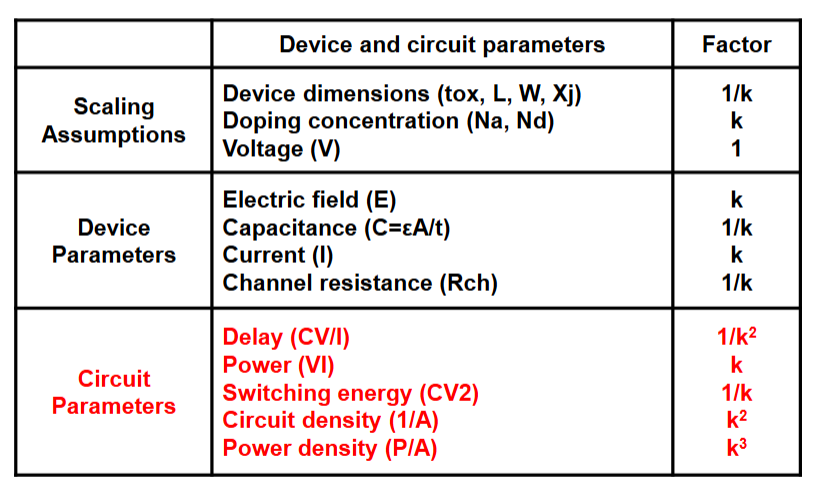

2.1 奇偶校验码(Parity Checking)

奇偶校验码一般是用来检测单比特错误,其原理是在数据中增添一个奇偶校验位,以此来确保二进制数据中的1的个数(包含奇偶校验位)为奇数或者偶数。

| 奇校验 | 偶校验 |

|---|---|

| 1的总数为奇数个 | 1的总数为偶数个 |

例如,在奇校验中,给定一串编码为11010100,可以看到该编码中1的个数为4个,是偶数个,因此需要增加一位校验位为1以此来使得这一串编码中1的总个数为5个,也就是奇数个1。如果在偶校验中,需要1的总数为偶数个,来看同样的一串编码11010100,因为其1的个数为4个,已经是偶数个,因此校验位只需要补0即可。

在硬件实现中如下图所示,采用异或门实现生成器与检测器:

思考:若换成奇校验,电路该如何变化?

注意:奇偶校验虽然可以检测单比特错误,但也仅限于此。该方法并不能检测偶数位错误,如果是多比特错误,它也只有50%的概率可以检测出。

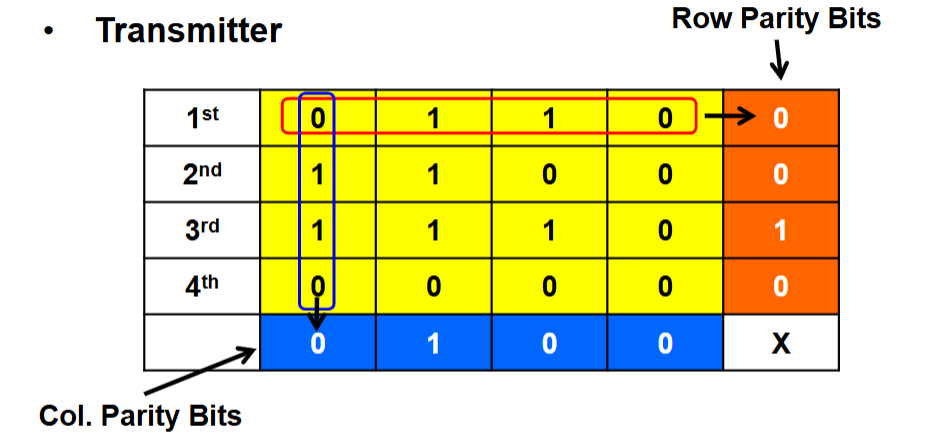

2.2 2D奇偶校验

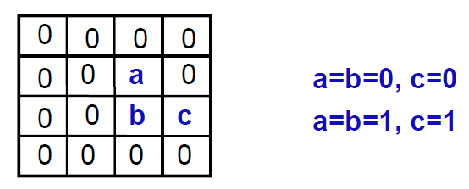

2D奇偶校验是在奇偶校验的基础上,将一维平面搬到了二维平面上,也就是新增加了列奇偶校验,这样便能够识别并且纠正单个比特的错误,并且可以检测到多比特错误,但是没法确定位置。

首先介绍在信号发送端中的2D奇偶校验原理:

其方法是将一串数据流以行列的形式进行排列,如上图,以奇校验为例,将0110 1100 1110 0000按照四行四列进行排列,然后对每行每列中1的个数进行统计,可以发现行奇校验位从上到下分别是0010,列奇校验位从左到右分别为0100,由此校验位全部确认完毕。

接下来是在接收端:

如上图,在接收端接收到发送来的数据后,也就是黄色框图的部分,其中出现一位错误,我们根据奇偶校验位是否合理即可推断出是哪一个位置的数据在传输中发生了错误。

注意:该方法可以检测并且纠正单比特错误,但多比特错误只能检测而无法知道错误位置所在,因此无法进行纠正。

2.3 汉明码(Hamming Code)

这里首先要知道汉明距离和最小汉明距离:

- 汉明距离:两个码字之间不同元素的数量

- 最小汉明距离:一组码字之间最小的汉明距离

- 如果汉明距离大于2,可以进行错误检测

- 如果汉明距离大于3,可以进行错误纠正

- 如果汉明距离大于4,则可以进行两位数据的错误检测

接下来对汉明码的原理进行解释:

对于

接下来就是对数据串和校验位进行编号排序,校验位按照

以 “101 0110” ,并且以奇校验规则为例进行讲解:

首先可以确定的是有7位数据,因此

所以列表如下:

| 位置索引 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 编码后的位置索引 | M7 | M6 | M5 | P4 | M4 | M3 | M2 | P3 | M1 | P2 | P1 |

接下来先将数据位按顺序填入表格中如下:

| 位置索引 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 编码后的位置索引 | M7 | M6 | M5 | P4 | M4 | M3 | M2 | P3 | M1 | P2 | P1 |

| 汉明码 | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

那么如何进行校验位的填充呢,新列一张表格进行解释:

| 位置索引 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 编码后的位置索引 | M7 | M6 | M5 | P4 | M4 | M3 | M2 | P3 | M1 | P2 | P1 |

| P1 (

|

|

|

|

|

|

|

|||||

| P2 (

|

|

|

|

|

|

|

|||||

| P3 (

|

|

|

|

|

|||||||

| P4 (

|

|

|

|

|

上图中,不同位置的校验位覆盖的范围是不同的。

对于在

可得P3和P4覆盖范围。

回到上面的例子中,我们现在知道了校验位的覆盖范围后,即可根据奇偶校验的规则对校验位进行填充数据。

例如P1,也就是

依此类推,P2为1,P3为1,P4为1,因此最终汉明码如下表所示:

| 位置索引 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 编码后的位置索引 | M7 | M6 | M5 | P4 | M4 | M3 | M2 | P3 | M1 | P2 | P1 |

| 汉明码 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 |

所以最后由奇校验规则以及数据串 “101 0110” 编码而成的汉明码为 “101 1011 1010”。

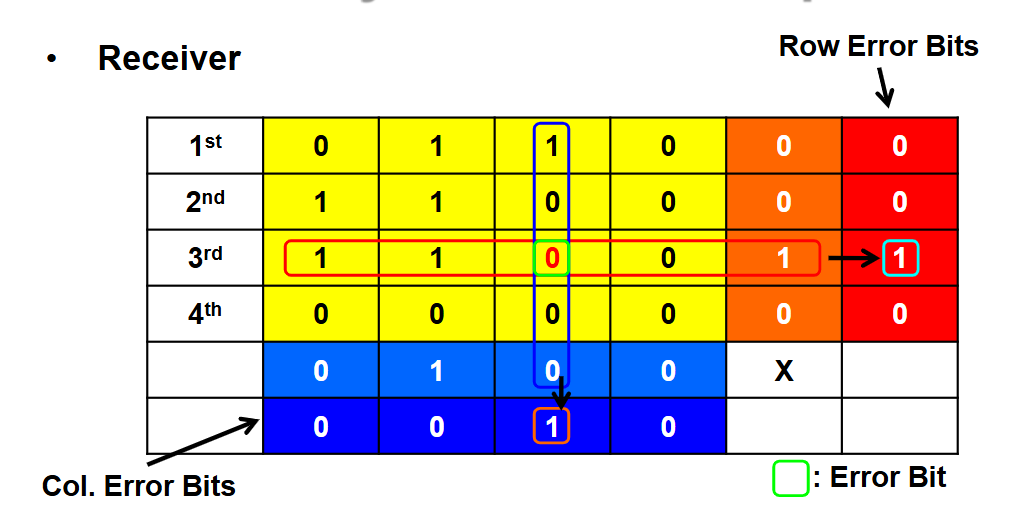

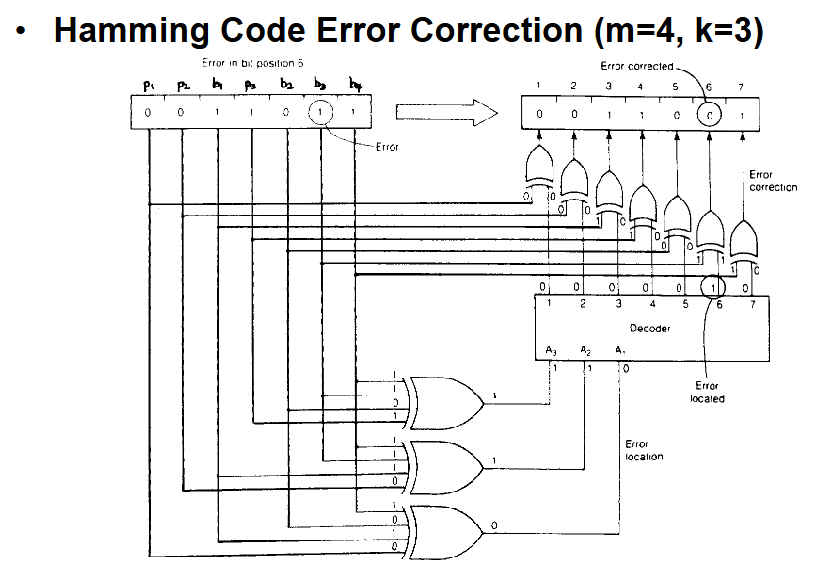

汉明码的硬件实现如下:

注意:使用汉明码进行错误检测和纠错时,需要注意其最小距离分别需要多少:

- 对于

- 对于

对于

- 编码效率

- 编码冗余

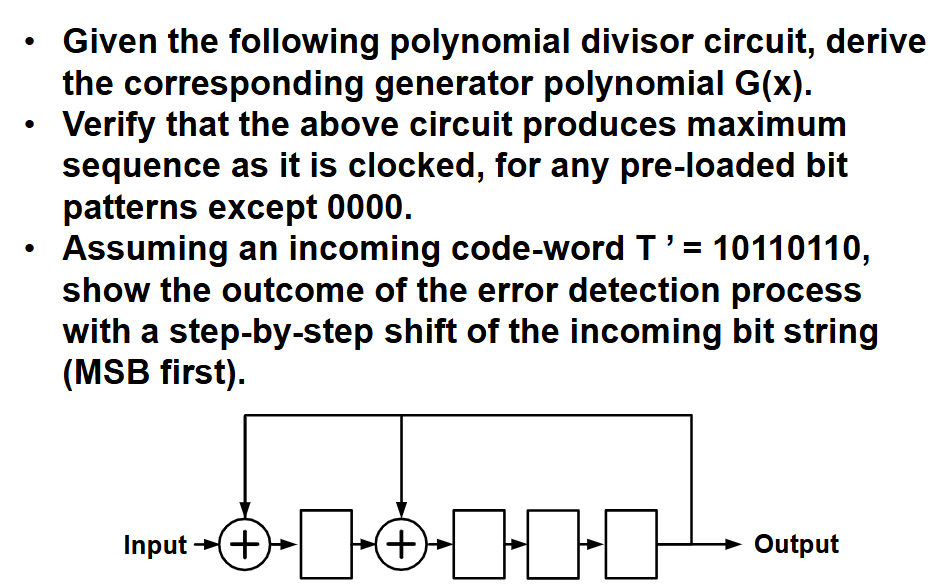

2.4 循环冗余编码(Cyclic Redundancy Check)

2.4.1 位置多项式

给定一个二进制比特串:

则其位置多项式可以表示为:

例如:数据串 "110 0101"就可以被表示为

2.4.2 CRC原理

首先我们需要先了解模2运算,其运算机制是:

- 每一位单独计算,没有进位也没有借位;

- 减法和加法是等价的(都是用异或运算实现)。

例如下图:

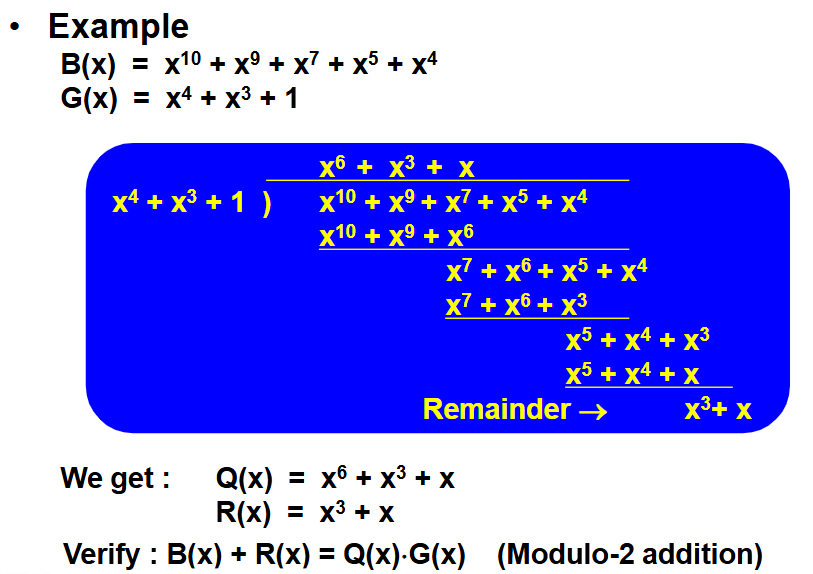

接下来,重点讲述CRC码的生成原理:

- 首先有一个给定的多项式

- 用生成多项式

- 传输

- 最后将原多项式

例子:现在有数据串

由

由数据串

然后用

所以

最后只需要在原数据串

注意:关于

2.4.3 多项式除法电路设计

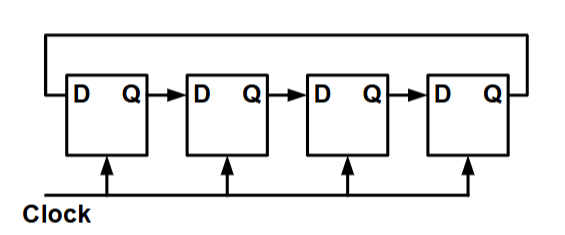

首先我们需要先对循环移位寄存器进行了解:

循环移位寄存器的输入是从左到右的,输入的数字在其中不断循环。在其反馈路径中添加一个异或门,即可使得循环的位模式发生变化。

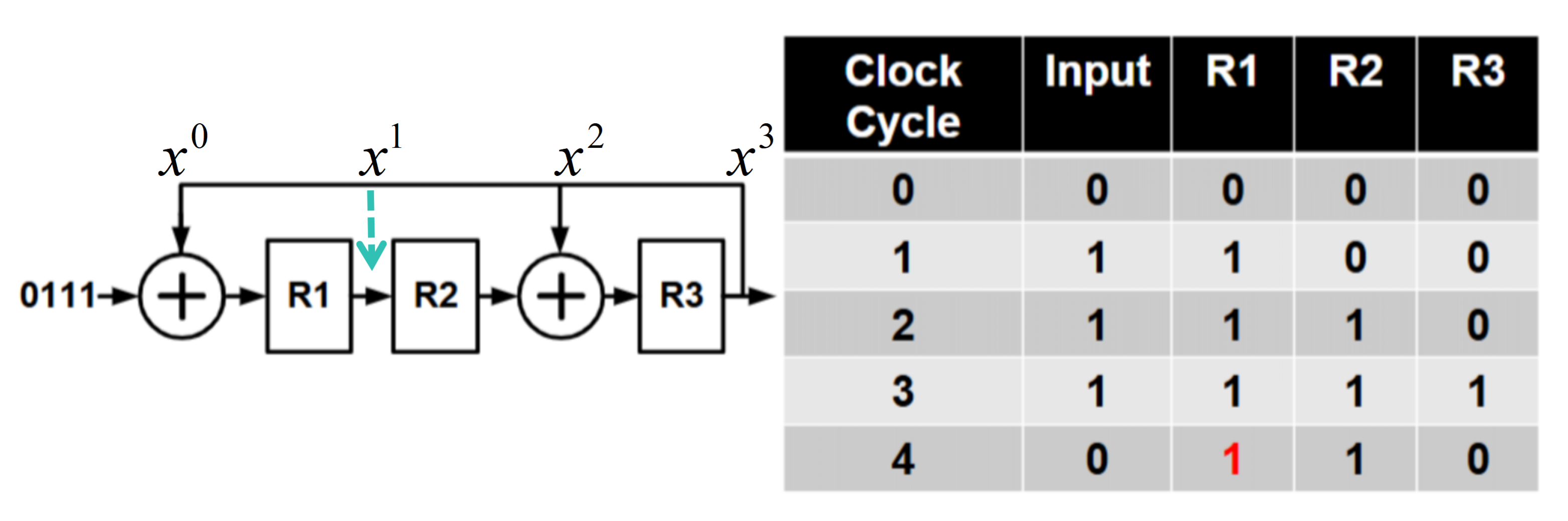

由此我们可以得到在实现CRC编码过程中得到的余数如何用电路实现:

对于原数据串为

从输入开始,每一个寄存器的左右(也就是会放置异或门的位置),分别是

就如上图,

考试例题如下:

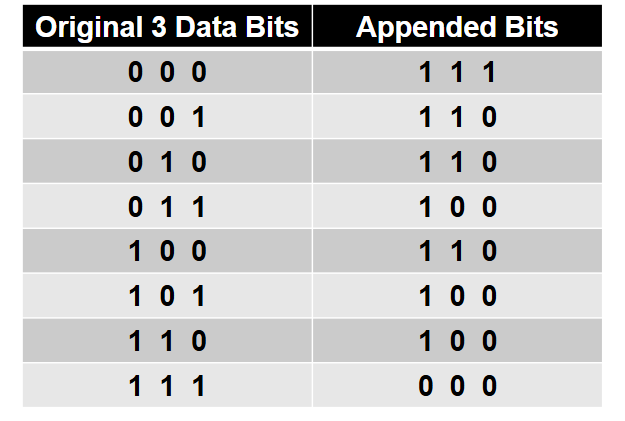

2.5 M-out-of-N Code

了解即可,感觉不会考,但以防万一还是讲解一下。

关于M-out-of-N Code,最简单的实现方式是在原始数据后附加一串 1,直到数据中包含

下面以3-out-of-6 Code来举例:

如上图所示,要保证1的数量一直为3个,而总数量是6个。

2.5.1 M-out-of-N校验器

对于一般的M-out-of-N检测器,可以将给定的码字转换为1-out-of-

而

其中,组合数计算公式为

以2-out-of-5 Code为例,关于其设计步骤如下:

- 将2-out-of-5 Code转换为1-out-of-10 Code

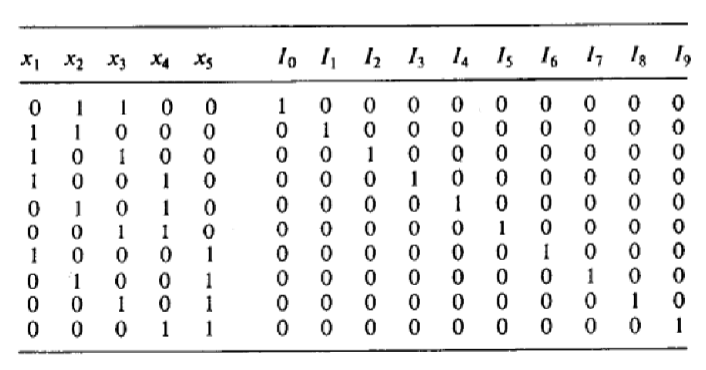

- 转换真值表如下图所示:

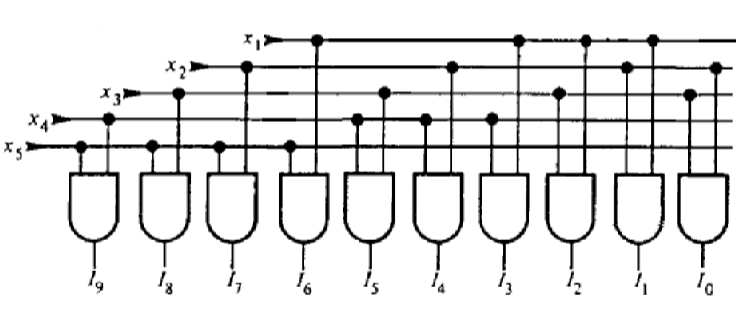

- 由此设计电路如下:

- 转换真值表如下图所示:

- 将1-out-of-10 Code 转换为3-out-of-6 Code

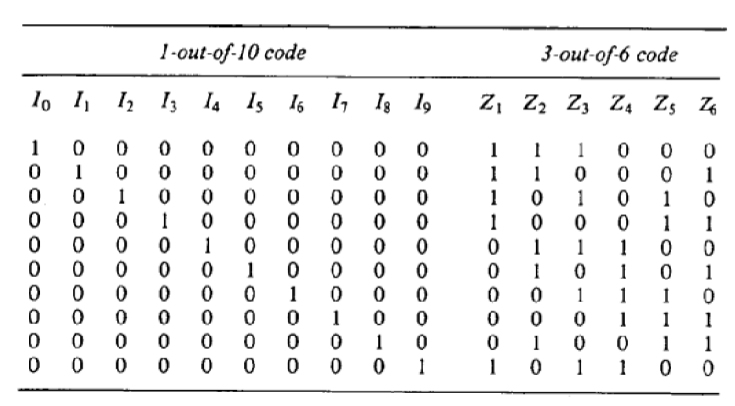

- 转换真值表如下图所示:

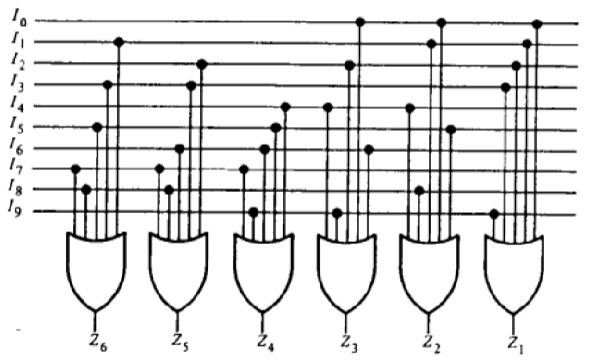

- 设计出的电路图如下:

- 转换真值表如下图所示:

- 设计3-out-of-6 Code 校验器

3 噪声考量(Noise Consideration)

3.1 特征阻抗(Characterisitic Impedance)

无损传输线路的特征阻抗可以从分布电感和电容推导得出,这里不做公式推导,直接给出公式:

同时传输速度公式如下:

另外,时间延迟即为传输速度的倒数,公式如下:

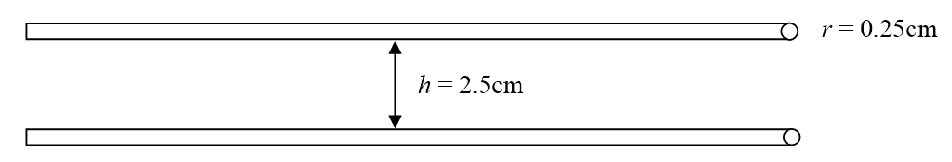

Example: 计算传输线的特征阻抗

Consider two round parallel wires of diameter 0.5cm and spaced 2.5cm apart with Teflon dielectric. Determine the characteristic impedance of these transmission lines. The relative dielectric constant of Teflon is 2.1. Discuss how the characteristic impedance will be affected if the diameter is increased to 1cm. Given that:

**Answer: **

Two round parallel wires of diameter 0.5cm and spaced 2.5 times their diameter apart with Teflon dielectric as follows:

**We know that: **

and according to

**Substituting the data yields:

Similarly, it can be obtained:

**When

3.2 反射(Reflections)

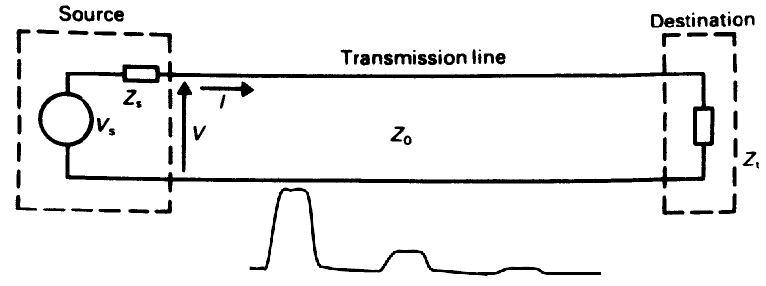

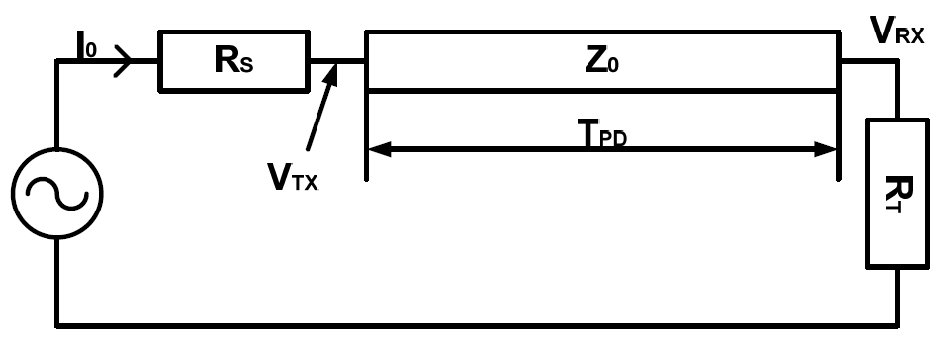

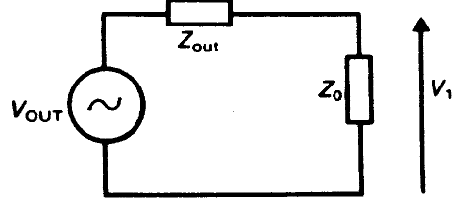

考虑一个 SOURCE端逻辑器件通过一条特性阻抗为

3.2.1 反射系数(Reflection Coefficient)

假设信号源从

在传输线的末端,终端的电压

若

因为

所以将上述式子整理后可以得到:

在上面的式子中,

又因为

或者:

注意:

这里需要了解三种极端情况:

- 当

-

-

- 因此,

-

- 当

-

-

- 因此,

-

- 当

-

-

- 因此,

-

因此,

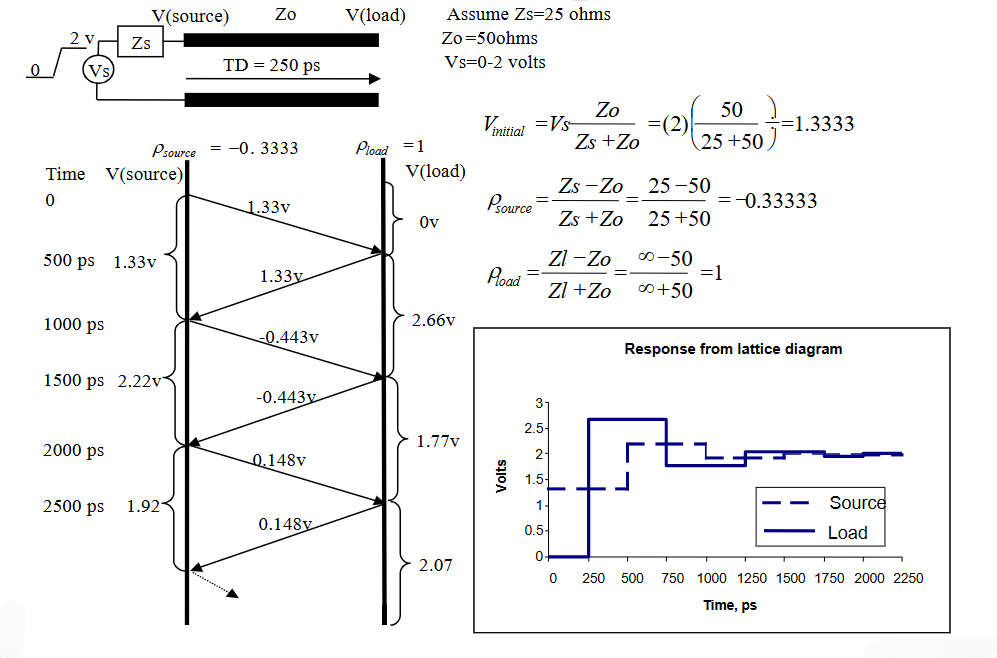

3.2.2 晶格图(Lattice Diagram)

- 晶格图是一种简化反射和波形计算的工具。

- 图显示了边界和反射系数。

- 时间轴垂直显示,计算每个连续反射波的电压幅度。

- 任何点的总电压是所有已通过的波的总和。

首先我们需要先明确晶格图的计算步骤:

- 先分析静态电路,也就是传输线两端的 $ V_{TX} $ 以及 $ V_{RX} $ 的初始值;

- 然后 计算传输线两端的反射系数 $ \rho_{source} $ 和 $ \rho_{load} $;

- 最后在计算施加在传输线上的初始发射电压 $ V_{launch} $

Example:

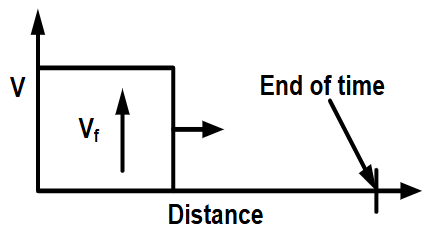

假设电源电压从

进行静态分析。由于此时电压波稳定,传输线不分压,因此:

然后进行动态分析,传输线此时分压,初始电压波传输到了传输线,所以初始的发射电压为:

然后在算出Source端和Load端的反射系数即可依顺序画出反射图。

关于晶格图,B站有个视频讲的很清楚,这里直接放上视频:

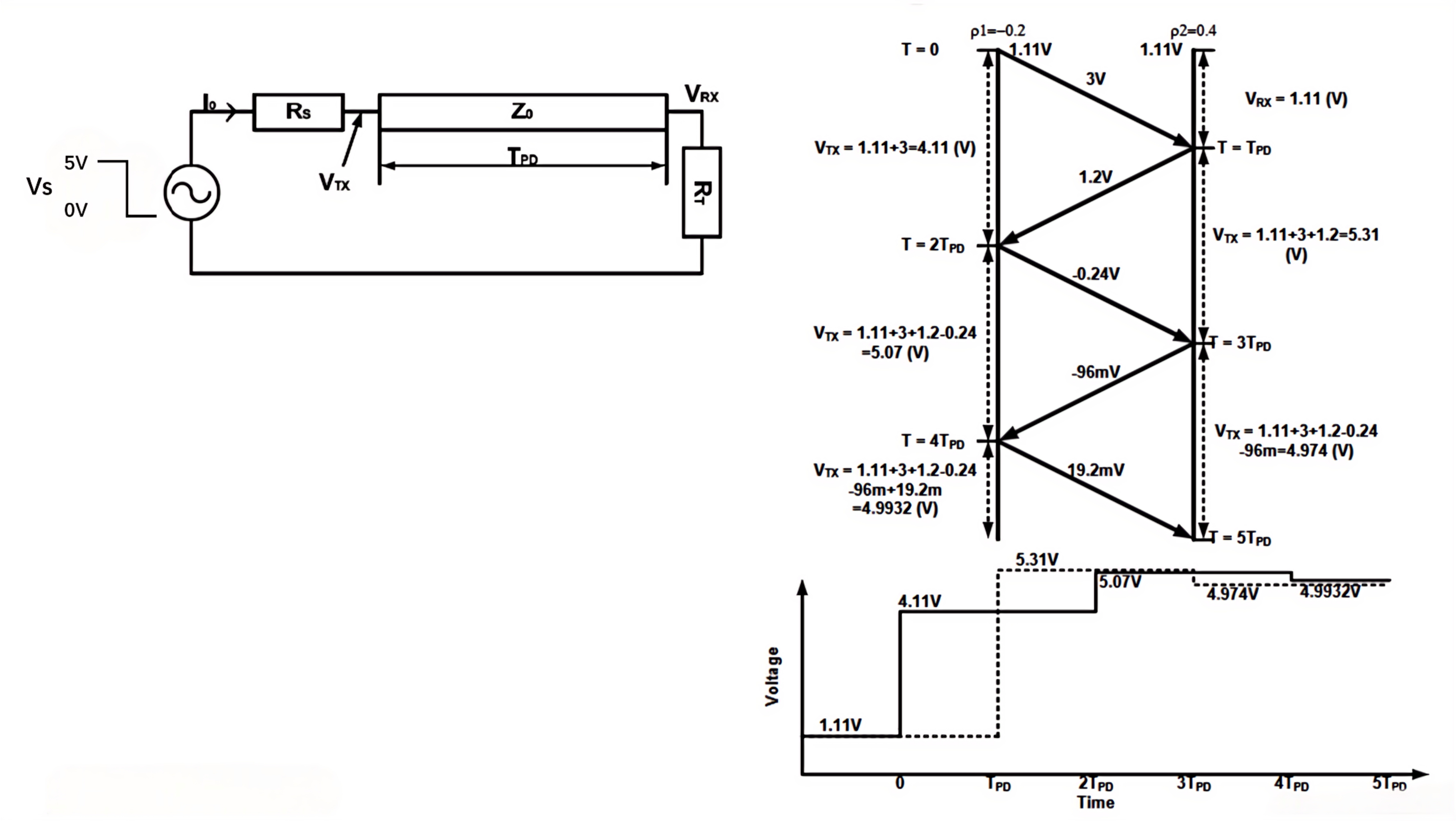

考试一般就考两种形式:一种是信号源从

下面分别给出第一道例题,信号源从

然后第二道例题是差不多的,但是由于信号源是从正向电压跳变到

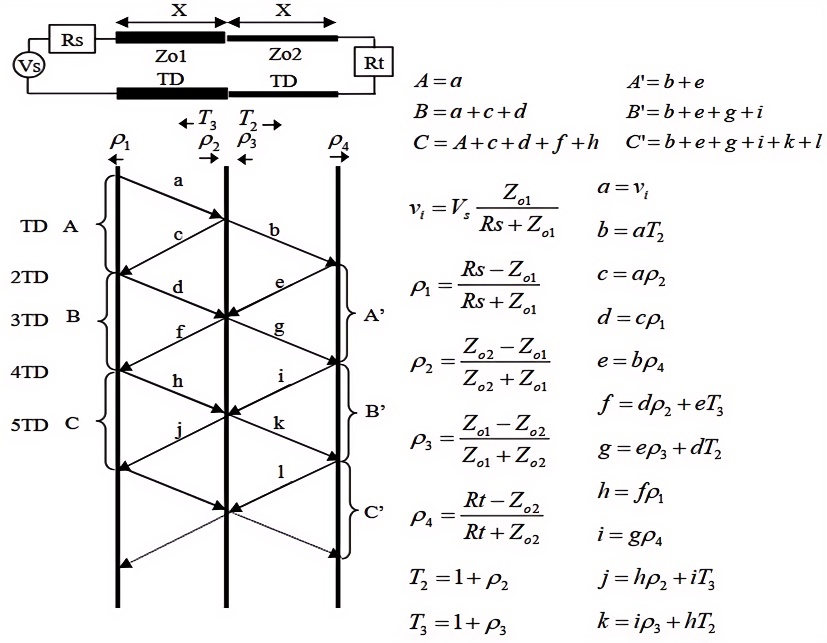

当波遇到特性阻抗不同的传输线之间的界面时,会同时产生反射波和透射波。透射信号是正向信号和反射信号的总和。这时的晶格图就变得较为复杂了,考试一般不考,但以防万一还是复习一下。其晶格图绘制如下:

3.2.3 减少反射的技术

如果下列阻抗都相同的话,就不会产生反射:

- 驱动门的输出阻抗

- 传输线的特性阻抗

- 接收门的输入阻抗

但是反射是不可能被完全消除的。

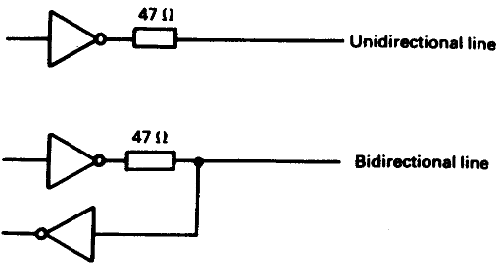

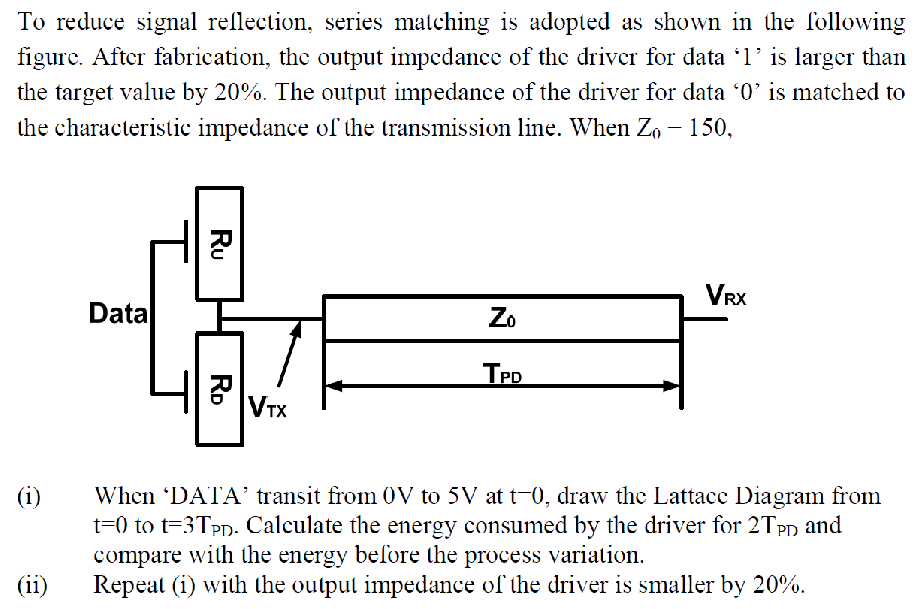

3.2.3.1 串行匹配(Series Matching)

第一种方法是采用**串行匹配(Series Matching)**来减少反射,那么串行匹配是如何减少反射,主要是以下几条:

- 人工增加输出阻抗以此来匹配传输线的特性阻抗

- 抑制负向过冲(“1”

- 使用外部串联电阻,典型值约为

另外,还需要知道功率消耗:

一个源端终端器一次往返的能量耗散为:

其中

当脉冲间隔大于往返延迟时,源端终端器的功耗为:

Example:

Answer:

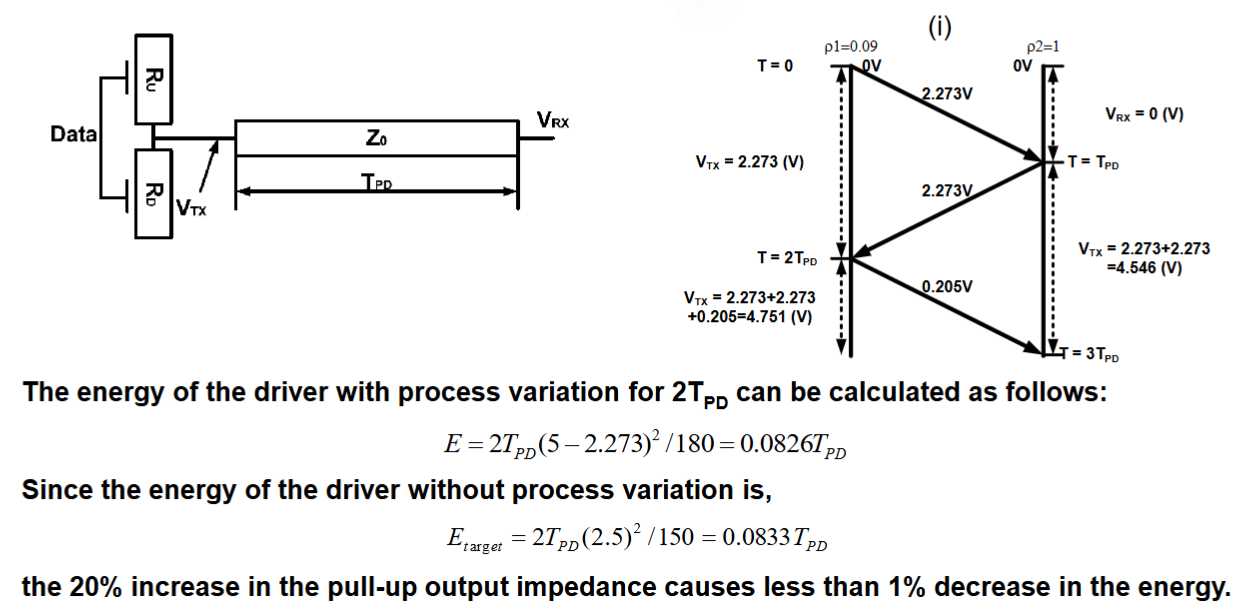

3.2.3.2 传输线终端处理(Line Termination)

第二种方法是采用传输线终端处理(Line Termination),主要手段是:

- 在总线系统中传输线的接收端进行匹配。

- 对于未端接和开放式的总线线路,可能会发生全值反射。

- 通过在总线末端放置电阻器来实现端接。

端接传输线的功耗:

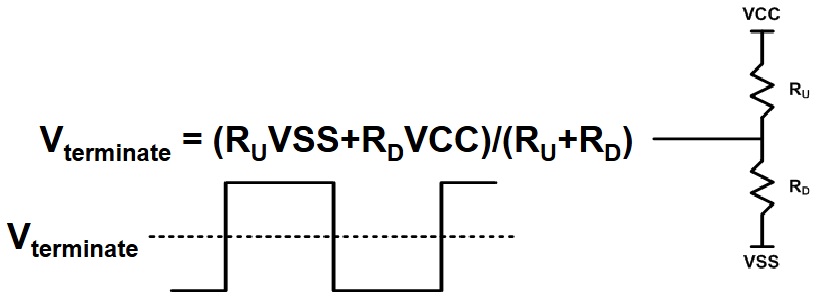

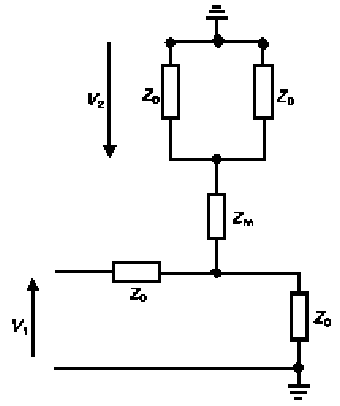

3.2.4 串扰(Cross talk)

一条信号线上的信号转换耦合到了相邻的线路上。这是由于两条相邻线路之间存在电容和互感,引发了磁场的相互作用,从而在受影响的线路上产生了反向电流,而这种现象就叫做串扰。

芯片上的导线与相邻导线(包括同层及相邻层)之间存在电容。

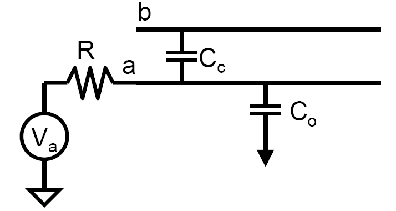

从上图,我们需要先知道

当相邻信号发生变化时,悬浮线上的电压会受到干扰,则它串扰用耦合系数衡量就是:

如上图,如果受害线

如果攻击线

也就是说,攻击线上的上升时间大于受害线的时间常数,则串扰就会减少。

3.2.4.1 串扰分析

使用单集总阻抗法(Single Lumped Impedance Approach)对串扰进行分析:

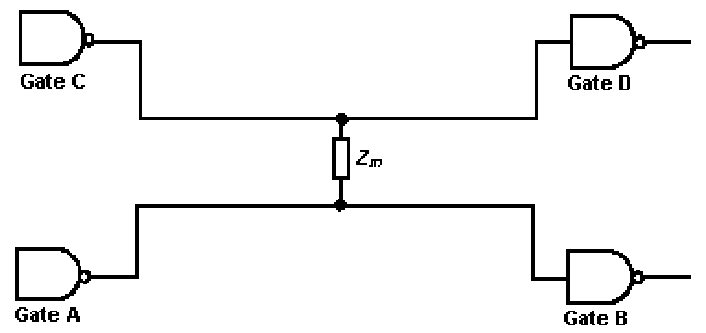

考虑两条线,中间有一个互阻抗

假设

单独分析攻击线,简单的分压得到传输线上的电压

所以门

注意:无论终端阻抗如何,门

随后分析受害线:

将互阻抗

整理后得:

代入

电压

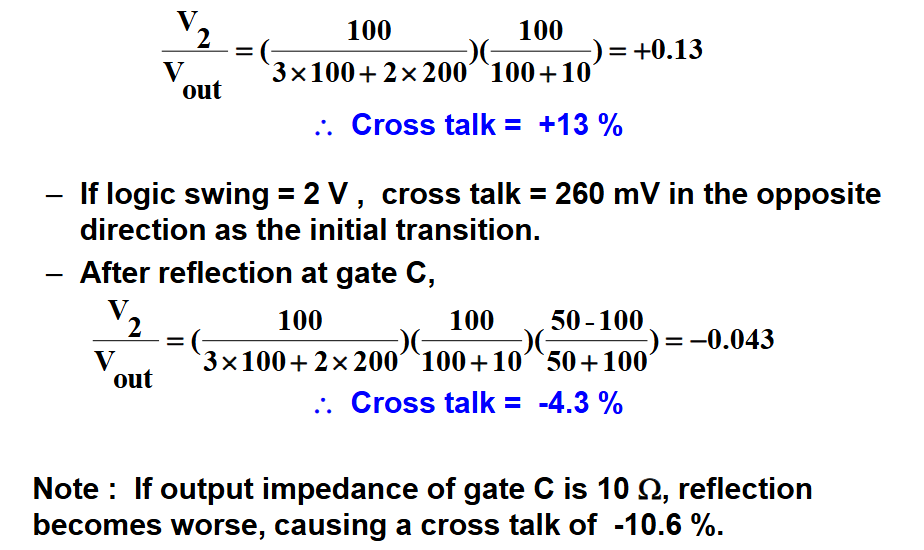

Example:

Consider gates

- A falling 1‑to‑0 transition occurs at the output of gate

- Gate

- Gate

- The characteristic impedance of lines

- The mutual impedance

Determine the level of crosstalk.

Answer:

3.2.4.2串扰的减小方法

3 种减小串扰的方法:

-

Reduce value of

-

Increase value of

-

Increase value of

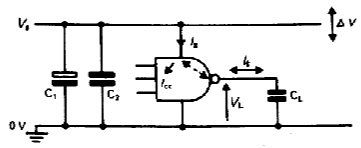

3.2.5 电源噪声

电流变化流过电源网络的寄生参数,导致电源电压波动,甚至会导致逻辑电平错误、器件误动作。

电源网络不是理想的,存在寄生元件:

- 片上寄生:金属线的寄生电阻

- 片外寄生:封装引脚、PCB 走线的寄生电感

流经这些元件的电流会产生噪声电压:

电源噪声的解决方法:去耦电容(Decoupling Capacitors)

相当于给电路配一个局部的小电池,在电流变化时快速提供或吸收电流,稳定电源电压。

- 接法:电容接在

- 作用:当逻辑门吸收电流时,电容放电提供电流,不让电源线上的电流突变,从而减小电源电压波动

Example 1:电容值的估算方法

74LS00 芯片,输入以 1MHz 方波翻转,电源 5V,允许电压波动 5%(

Solution:

公式如下:

所以,

Example 2:决高频瞬态尖峰的电容

瞬态电流

Solution:

则可以得到:

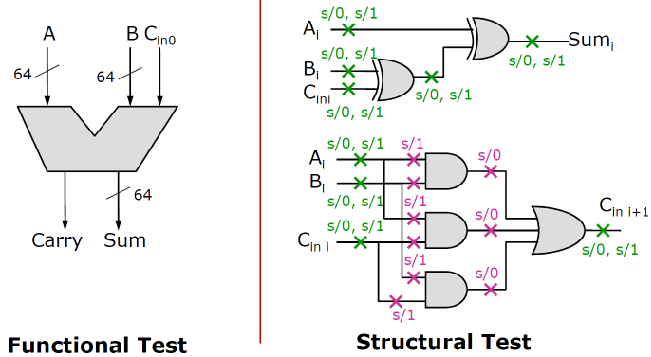

4 Fault Models(故障模型)

测试面临的问题是,如何用最少的测试模式去获得最高的故障覆盖率。

测试流程

- 要测试哪些故障?(fault modeling)

- 如何获得测试模式?(test pattern generation)

- 如何测量故障覆盖率?(fault simulation)

- 如何应用测试向量和评估结果?(ATE/BIST)

4.2 故障类型

4.2.1 按故障性质分类

- 逻辑故障 。一个导致电路元件的逻辑功能更改为其他功能;

- 参数性故障。指改变电路参数大小, 导致电阻、电容、电流等因素发生变化的故障。

- 延迟故障。一种与电路延迟相关的问题, 如门电路速度慢, 通常会影响电路的时序, 可能导致冒险或性能下降等情况。

4.2.2 按故障持续时间分类

-

永久性故障。一种持续且稳定的持久性故障, 其性质在测试前、测试中和测试后均不发生变化。例如, 断线、错误的焊接等。亦称硬故障或固定故障;

-

临时故障

一种仅间歇性出现的故障, 它在随机时刻发生, 并在有限但未知的时间段内影响系统。

- 转换故障由环境条件引起, 例如宇宙射线、 α 粒子等。在 RAM 中也被称为软错误;

- 间歇性故障由非环境条件引起, 例如组件参数的边际值、磨损或关键时序;

4.3 故障建模

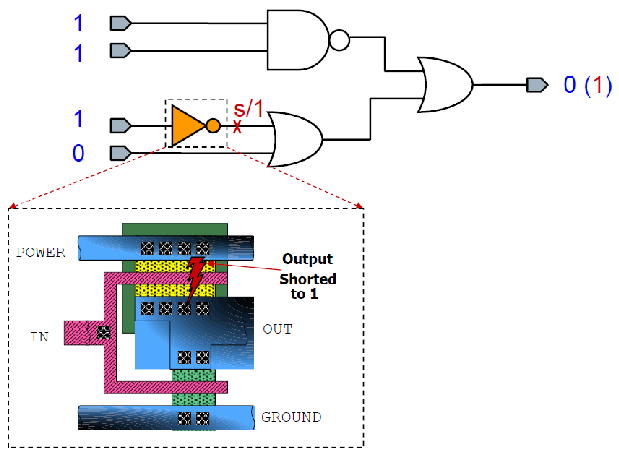

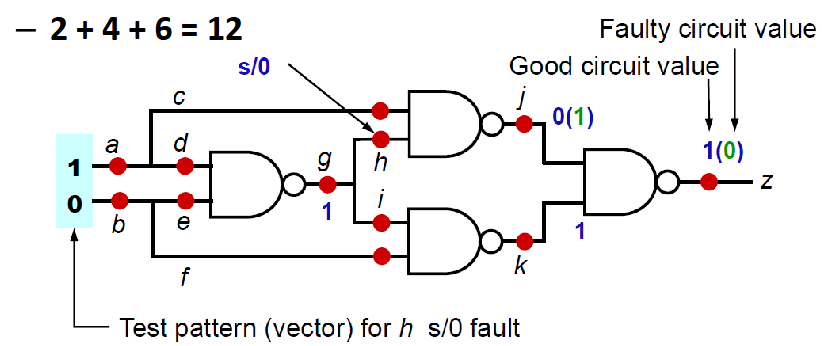

4.3.1 Single Stuck-At Fault(单线固定故障)

SSA就是指给定线路具有恒定值 (0/1),与电路中其他信号值无关。

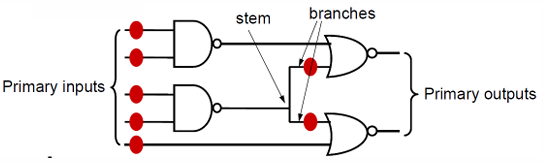

在数字电路测试中,故障点(Fault Site) 是指电路中可能发生逻辑故障的物理或逻辑位置。对于一个布尔门级电路,故障点的总数通常由以下三部分组成:

其中:

- #

- #gates:电路中的逻辑门数量;

- #Fanout branches:电路中所有扇出分支(

Example:

XOR circuit has 12 fault sites (•) and 24 single stuck-at faults:2 + 4 + 6 = 12

4.3.2 Multiple Stuck-At Faults(多重固定型故障)

Multi Stuck-At 指多个单固定型故障同时发生。实践中通常不考虑多重固定型故障, 原因有下面两点:

- 在含有 k 个节点的电路中, 多重固定型故障的数量线数为

- 当电路规模较大且具有多个输出时,针对单固定型故障的测试已知能覆盖很大高比例 (大于 99.6% ) 的多重固定型故障;

4.3.3 Switch-level fault models(开关级故障模型)

开关级故障模型描述的是开关级电路描述中的晶体管故障。这种故障模型主要用于 MOS 技术,特别是 CMOS 技术。此类别中最常见的是 stuck-open 和 stuck-on 故障模型。

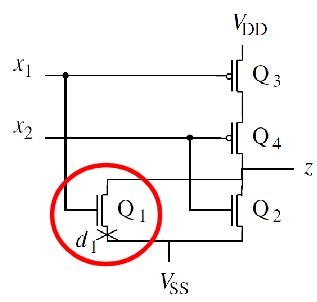

4.3.3.1 Stuck-open fault model, SOpF(固定开路故障模型)

因某种缺陷导致晶体管永久截止:

假设如下序列:

缺陷

当输入组合

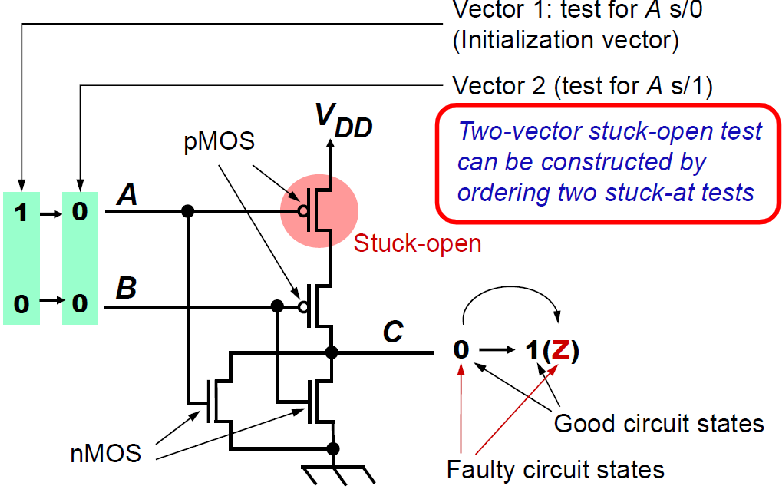

固定开路故障检测需要一组测试向量序列

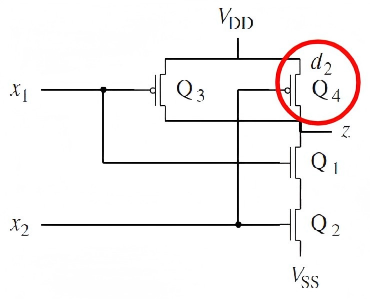

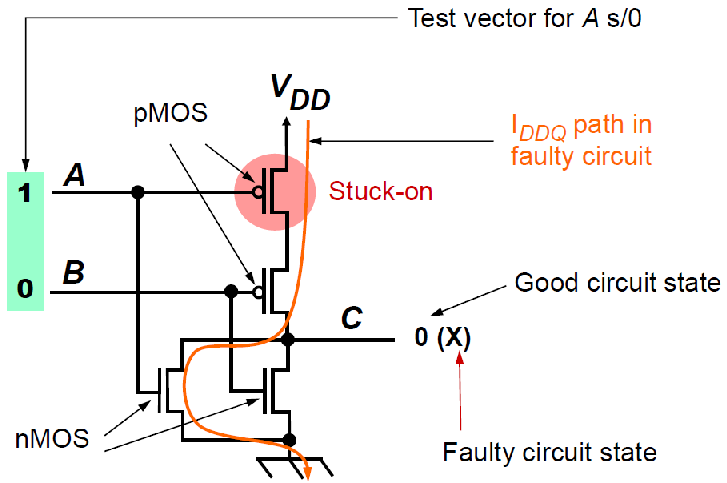

4.3.3.2 Stuck-on fault model, SOnF(固定导通故障模型)

因故障缺陷导致晶体管永久导通:

缺陷

施加至与非门的唯一输入向量为(1, 1; 0):故障存在时,晶体管

用 CMOS 电路在稳定状态时,从电源到地的直流电流对故障进行测试。如示例所示,A 给 1 信号,B 给 0 信号,正常来说应该输出 0;如果输出

4.3.4 Geometric Fault Model(几何故障模型)

- 直接源自电路布局

- 利用线宽、线间距离、元件间距以及器件几何结构相关知识,判定最易出现的缺陷类型

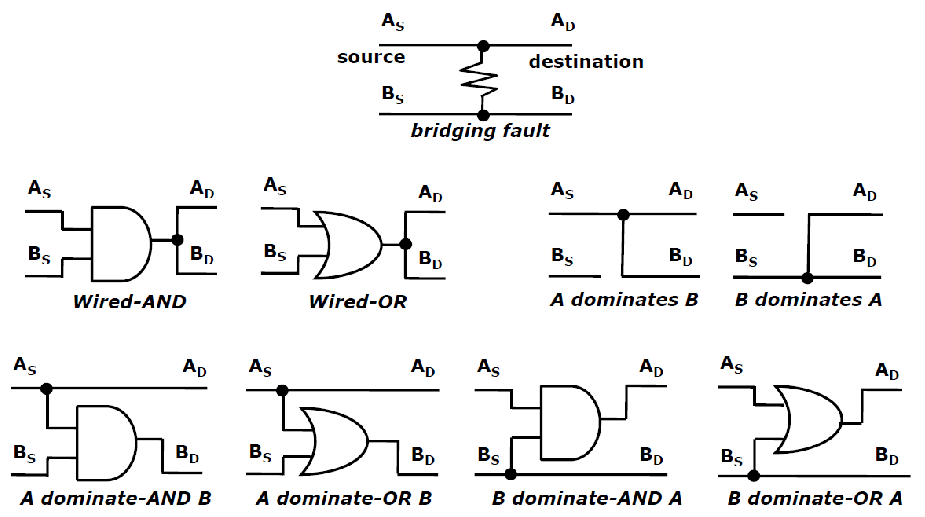

- 桥接故障(BFs):引发短路的缺陷占比

- 线与:两条线路形成与逻辑功能

- 线或:两条线路形成或逻辑功能

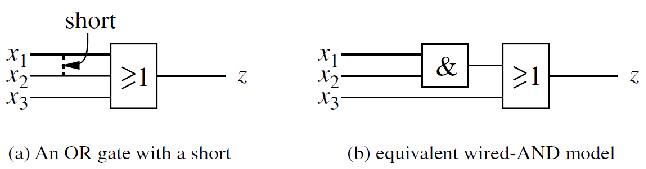

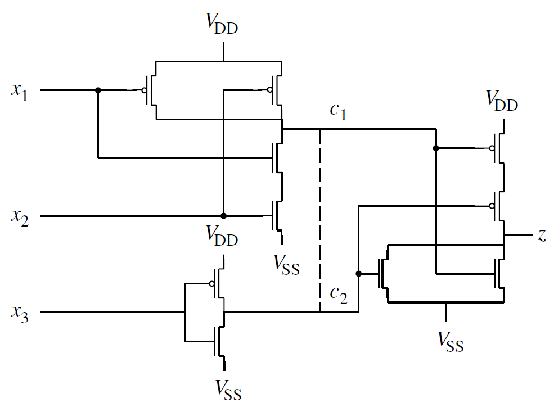

Consider the short between C1 and C2. For

4.3.4.1 Bridging Faults(桥接故障)

桥接故障就是两个或多个原本相互独立的节点 (线路) 发生短路连接

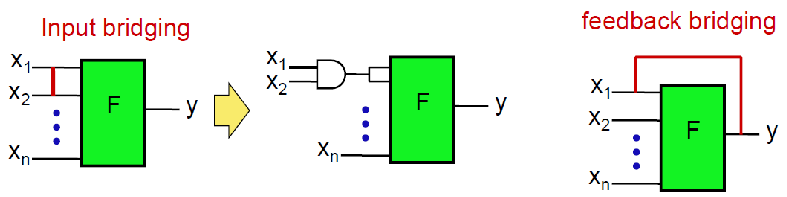

桥接故障分为两类:

- 输入桥接

- 可形成线逻辑或表决电路模型

- 反馈型(输入至输出)桥接

- 会引入反馈回路

- 可能引发电路振荡或锁存效应(产生额外存储特性)

4.3.5 Pattern-Sensitive Faults(状态依赖型故障)

故障信号的出现取决于邻近节点的信号值,该故障在动态随机存取存储器(DRAM)中最为常见。

耦合故障就是存储单元两两之间存在模式敏感性。

4.3.6 Single Cell Fault(单元故障)

单元故障是单元自身的、无条件的、和其他单元完全无关的硬失效。

- 故障只发生在这个单元本身,不管周围其他单元是什么数值、什么状态,这个单元的故障都永久存在。

- 例如:

- 存储器单元的固定型故障(stuck-at 0/1):这个单元永远只能读出 0,不管你写入 0 还是 1、不管邻居单元是 0 还是 1,它都坏了。

- 行波进位加法器:某个全加器(FA)自身的逻辑门坏了,不管前后级全加器的输入是什么,它的输出永远错误,和其他单元无关。

- 核心特点:测试难度极低,具备C-可测试性 — 测试向量的数量是固定的,和电路 / 存储器的规模无关(比如不管多少位的加法器,8 个测试向量就能覆盖所有单单元固定故障)。

4.3.7 Delay Fault(延迟故障模型)

故障可能仅影响电路的时序特性,而非其逻辑功能,简单来说就是路径(门电路)上的传输延迟超出规定范围。

- 门延迟故障(Gate delay fault, GDF):逻辑门的输入端或输出端存在集中式延迟故障,表现为

- 严重门延迟故障(Gross gate delay fault, G-GDF):延迟缺陷时长大于时钟周期,会造成毁灭性故障。

- 轻微门延迟故障(Small gate delay fault, S-GDF):延迟缺陷时长小于时钟周期,至少一条通路出现时序失效,需对每条通路进行两次检测测试。

- 路径延迟故障(Path delay fault, PDF):电路中存在某条信号通路,其

4.3.7.1 延迟故障测试

- 无冒险健壮测试(Hazard-free robust test, HFRT):无论门延迟取值如何,被测通路均不会产生冒险现象

- 非无冒险健壮测试(Non-hazard-free robust test):被测通路上存在冒险

- 多通路传输(Multiple-path propagating, MPP):延迟故障测试通过多条通路将跳变信号传输至输出端

- 单通路传输(Single-path propagating, SPP):跳变信号仅通过单一通路完成传输

- 单输入变化(Single-input change, SIC):从初始化向量到测试向量,仅有一个输入信号发生改变

- 多输入变化(Multi-input change, MIC):从初始化向量到测试向量,多个输入信号发生改变

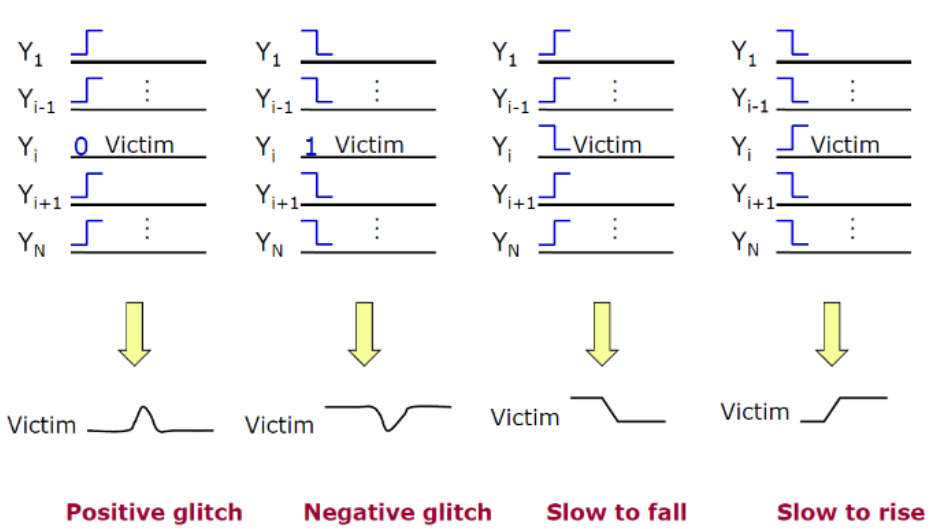

4.3.7.2 跳变延迟故障(Transition Delay Fault)

跳变延迟故障就是指逻辑门输出可能出现上升缓慢或下降缓慢的情况,且该延迟时长超出预设阈值。

若延迟故障的影响足够严重,跳变延迟故障会表现为固定型故障,可采用固定型故障的建模方式进行分析。

跳变延迟故障的主要缺陷:

-

需要两组时序序列,分别完成电路初始化与跳变检测工作;

-

受时序竞争冒险问题影响,难以界定可实现的最小延迟故障范围;

因此,工程中通常会直接采用完整的任务时钟周期开展相关设计与检测。

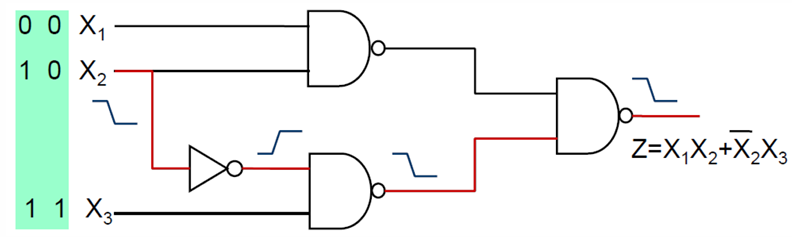

4.3.8 串扰故障(Crosstalk Defects)

电容串扰噪声源于两条信号网络之间的寄生耦合

4.4 测试和测试向量(Test and Test Set)

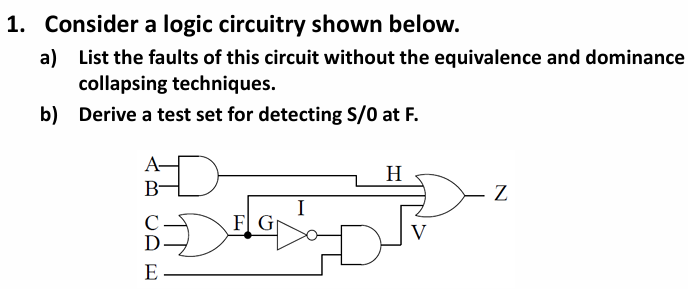

这一节内容一定是必考的:

电路

-

也被称作测试图形或测试向量;

-

若输入

针对故障集合 A 的测试集,是一组测试用例集合 T,满足:

-

对于

-

单一故障 α 的测试集为

-

举例说明:

-

这里

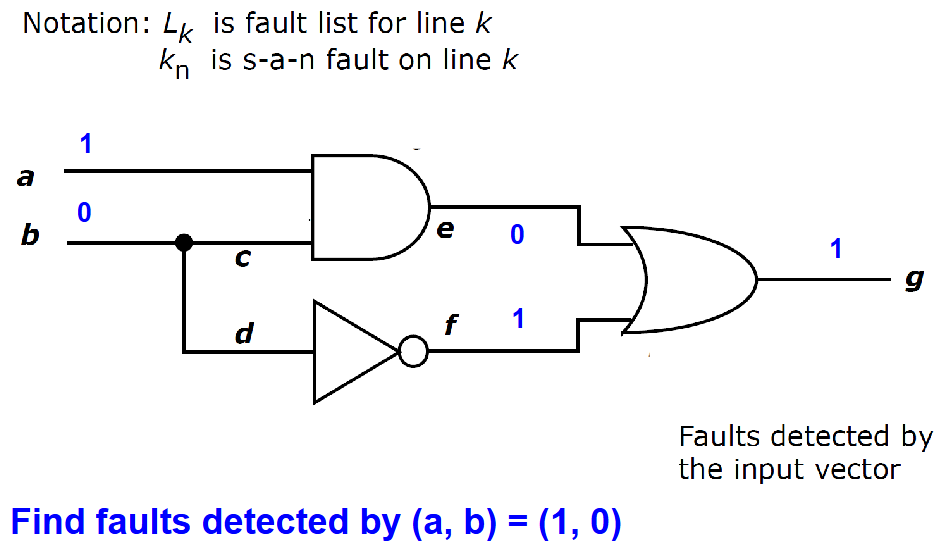

Example:

(1) "检测到故障"的核心标准:用这个输入时,故障电路的输出和正常电路的输出不一样

我们看测试输入(1,0):

- 正常电路的正确输出是

1; - 如果有

a/0故障,实际输出是0,和正确结果不一样 → 能检测到a/0故障; - 如果有

c/0故障,实际输出是0,和正确结果不一样 → 也能检测到c/0故障。

所以(1,0)这个测试输入,能同时测出这两个故障。

(2) 一个测试输入只能测出"有没有故障",但没法区分是a/0还是c/0,所以我们再加一个测试输入(0,1),用两个输入就能精准定位故障。

先看测试输入(0,1):

- 正常电路的正确输出是

1; - 对于

a/0故障:输入是0和1,a本来就是 0,故障不影响,输出还是1,和正确结果一样,没有故障表现; - 对于

c/0故障:输出还是0,和正确的1不一样,有故障表现。

Practice:

4.5 故障压缩(Fault Collapsing)

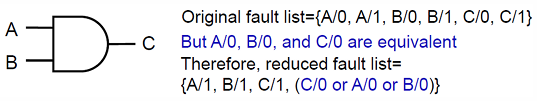

4.5.1 Equivalent Fault Collapsing(等效故障压缩)

如果每一个能检测出一个故障的模式也能检测出另一个故障, 则称这两个故障是等效的。

例如:

- 与门:所有

s/0故障等效; - 或门:所有

s/1故障等效; - 对于一个 输入的门电路,通过等效故障压缩,仅需要考虑

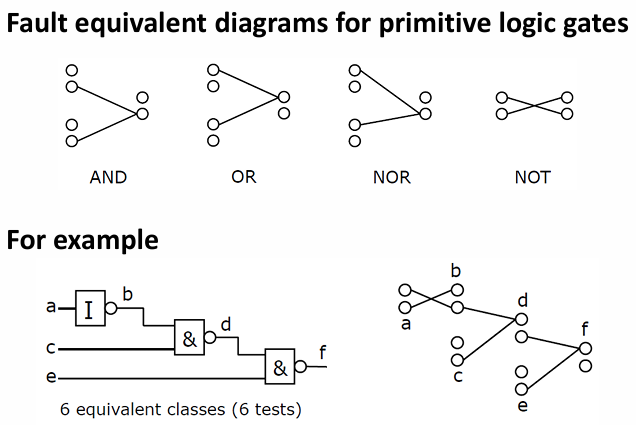

我们需要掌握如何用故障图压缩:

- 用一对圆圈表示每条线

x:上方圆圈代表x取值为x/1,下方圆圈代表x取值为x/0 - 若两个圆圈互为等价关系,则用一条边将二者相连

- 图中的每个网络对应唯一的故障等价类

-

a/0故障:a永远固定为0。只有输入(1,1)时,正常电路输出是0;故障下a=0,输出是1,和正常结果不一样。(1,1)。 -

b/0故障:b永远固定为0。同理,只有输入(1,1)时,才能测出故障。(1,1)。 -

c/1故障:输出c永远固定为1。只有输入(1,1)时,正常输出是0,故障下还是1,才能测出故障。(1,1)。

这三个故障,能测它们的测试输入完全一样,所以是等价故障,用线连起来,归成一个等价类{a/0, b/0, c/1}。

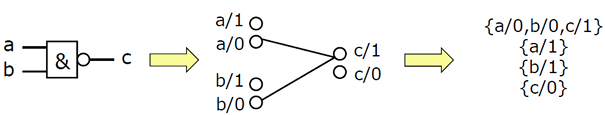

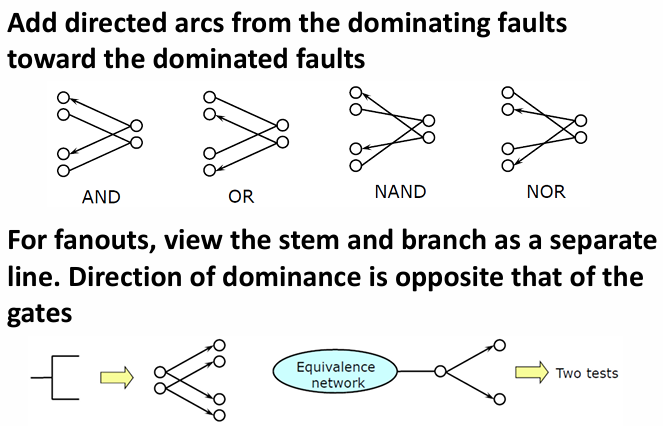

4.5.2 Dominance Fault Collapsing(支配故障压缩)

对于两个故障 f1 和 f2:

如果所有能检测到 f2 的测试向量,也一定能检测到 f1,那么我们说:f2支配f1,或者说f1被f2支配。

被支配的故障f1可以直接从故障列表中删掉,因为只要测了支配它的故障f2,就等于也测了 f1。

我们以 2 输入与门举例,看看支配关系是怎么来的:

-

与门逻辑:

C = A AND B,只有a和a都为1时,输出C才是1;其他情况输出都是0。 -

故障:输入的

s/1故障(永远固定为1)和输出的c/1故障(永远固定为1)。-

要检测输入

a/1故障,我们需要输入(0,1):正常输出是0,故障下a=1,输出变成1,和正常结果不一样。 -

这个测试向量

(0,1)同时也能检测输出c/1故障:正常输出是0,故障下c永远是1,输出也不一样。

也就是说,所有能检测

a/1或b/1的测试向量,都能检测c/1。 -

-

所以:

a/1和b/1支配c/1,c/1是被支配故障,可以从故障列表中删掉。- 原来的故障列表:

{a/0, a/1, b/0, b/1, c/0, c/1} - 删掉被支配的

c/1后,变成:{a/0, a/1, b/0, b/1, c/0}(再结合等价压缩,最终可进一步减少)。

- 原来的故障列表:

规律总结:

- n 输入与门(AND/NAND):输出的

stuck-at-1故障,会被所有输入的stuck-at-1故障支配,因此输出的1故障可以删掉。 - n 输入或门(OR/NOR):输出的

stuck-at-0故障,会被所有输入的stuck-at-0故障支配,因此输出的0故障可以删掉。

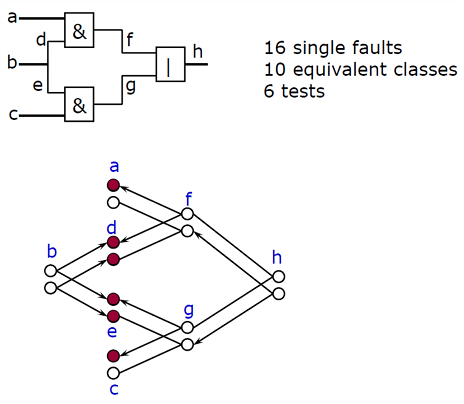

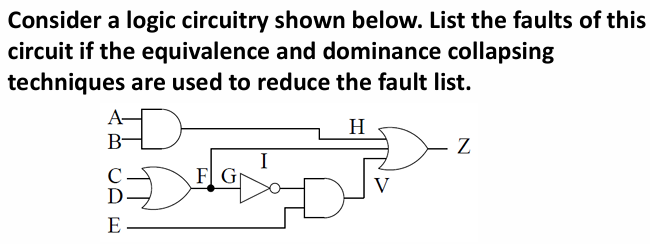

Example:

等价故障合并和支配故障合并 — 对于任意 n 输入门,仅需考虑 n+1 个故障;

测试压缩是指在不降低故障覆盖率的前提下,精简测试集中测试向量数量的过程 — 等价故障合并与支配故障合并可辅助实现测试压缩;

定理:在无扇出组合电路中,凡是能够检测出所有原始输入固定故障的测试集,均可检测全部固定型故障。

- 所有原始输入与所有扇出分支的集合,统称为电路的检测点。

- 在组合电路中,能够检测出检测点上所有单(多)固定型故障的测试集,可检测出全部单(多)固定型故障。

Practice:

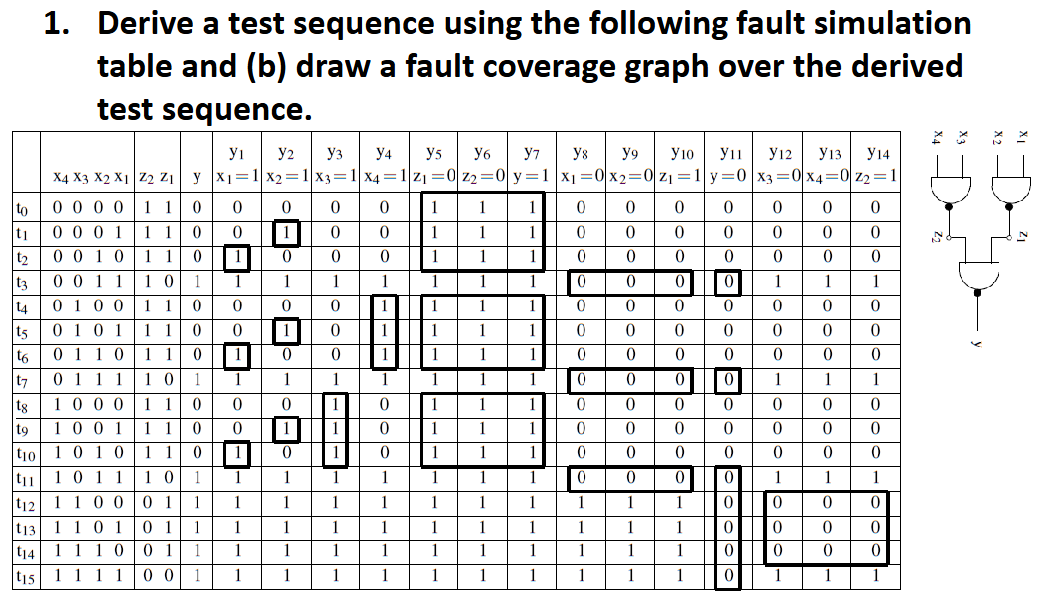

5 Fault SimulationI and Test Generation(故障仿真与测试生成)

5.1 仿真

仿真本质就是对芯片设计的功能、性能进行软件建模,在计算机上模拟芯片实际工作的电气与逻辑行为。简单来说,就是在电脑里“造一个虚拟的芯片”,给它施加和真实工作一致的输入,看它的输出是否符合预期,提前发现设计中的bug。

仿真的核心目标是设计验证(Design Verification),具体分为三个维度:

- 验证设计假设(Validate assumptions):在架构设计阶段,验证系统方案、架构选型的合理性,比如总线带宽、流水线性能是否满足需求。

- 验证逻辑功能(Verify logic):确认设计的逻辑行为完全符合规格书,比如加法器的运算结果、状态机的跳转是否正确,这是最基础也最核心的仿真环节。

- 验证时序性能(Verify performance (timing)):模拟门电路、互连线的延迟,确认芯片在目标频率下,寄存器的建立时间、保持时间等时序要求全部满足,避免出现亚稳态、时序违例。

5.1.1 编译式仿真

- 第一步:将组合逻辑分层,并用可编译的编程语言进行编码;

- 第二步:初始化内部状态变量 (触发器)

- 第三步:对于每个输入向量,设置主要输入变量,重复 (直到达到稳态或最大迭代次数),执行编译后的代码,报告或保存计算变量。

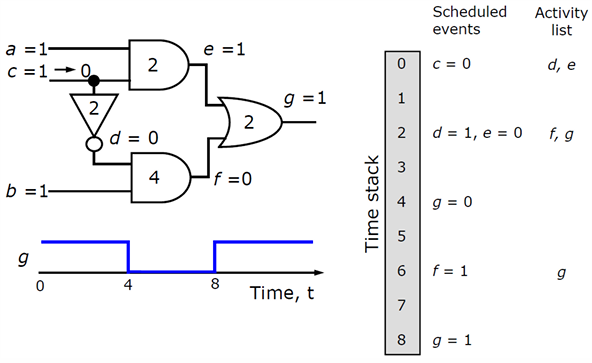

5.1.2 事件驱动式仿真

- 仅对产生输入事件的门电路或模块进行运算评估

- 可精准模拟电路延迟,满足时序验证需求

- 针对低活跃度电路仿真性能优异

- 可拓展适配故障仿真场景

事件驱动仿真器的效率:

- 仅对事件(数值变化)进行仿真

- 相比编译代码,运行速度可提升十倍及以上;在大型逻辑电路中,单次输入变化仅会有约 0.1% 至 10% 的门电路处于工作状态

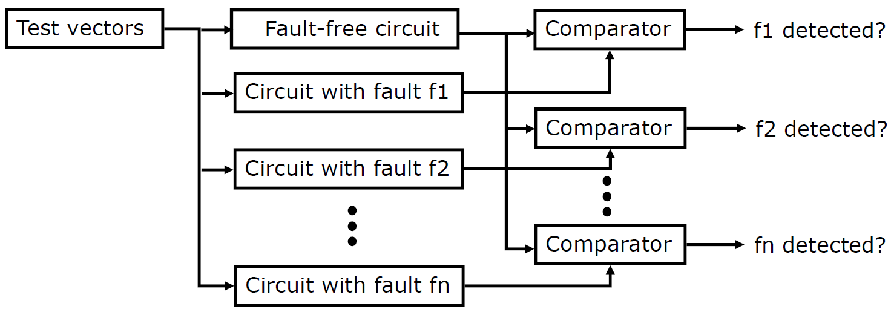

5.2 故障仿真范式

5.2.1 Serial Fault Simulation(串行故障仿真)

仿真无故障电路并保存响应结果。针对故障列表中的每一项故障,重复执行以下步骤:

- 通过注入单个故障修改网表

- 逐向量仿真修改后的网表,将输出响应与已保存的响应数据进行比对

- 若响应结果存在差异,判定故障被检测到,并暂停后续向量的仿真流程

Advantage:

- 实现方式简单,仅需真值仿真器即可完成

- 内存占用需求更低

Disadvantages:

- 大量重复计算

- 超大规模集成电路的中央处理器耗时过高、难以实现

替代方案,同时仿真多种故障。

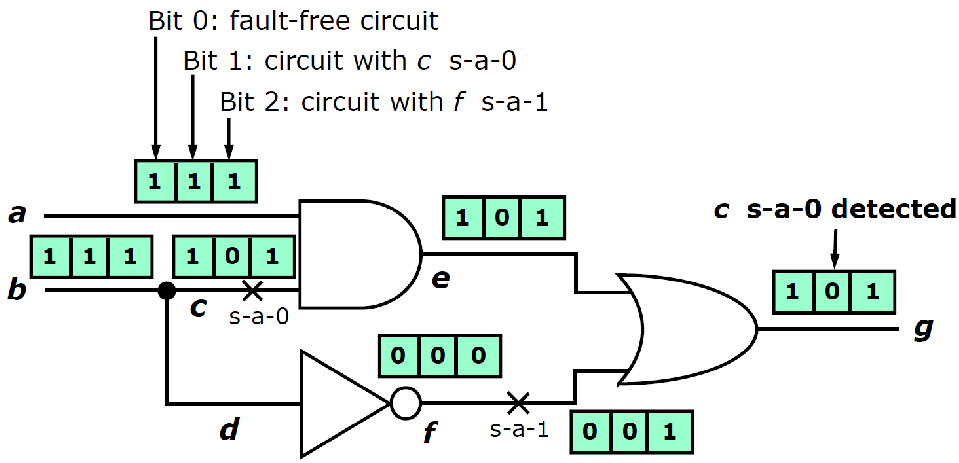

5.2.2 Parallel Fault Simulation(并联故障仿真)

假设仿真电路仅由逻辑门构成, 且所有门具有相同的延迟;信号仅取二进制值 ( 0 和 1 )。

利用数字计算机中逻辑运算的位并行性。对于 32 位机器字,一个整数由 32 位二进制向量组成。涉及两个字的逻辑 AND 或 OR 运算对所有相应的位对同时执行 AND 或 OR 运算

存储要求:二态仿真模式下,每一行占用一个机器字。

如果计算机字长为

缺点:

- 无法精确模拟信号上升和下降的延迟

- 不适用于非布尔逻辑电路。

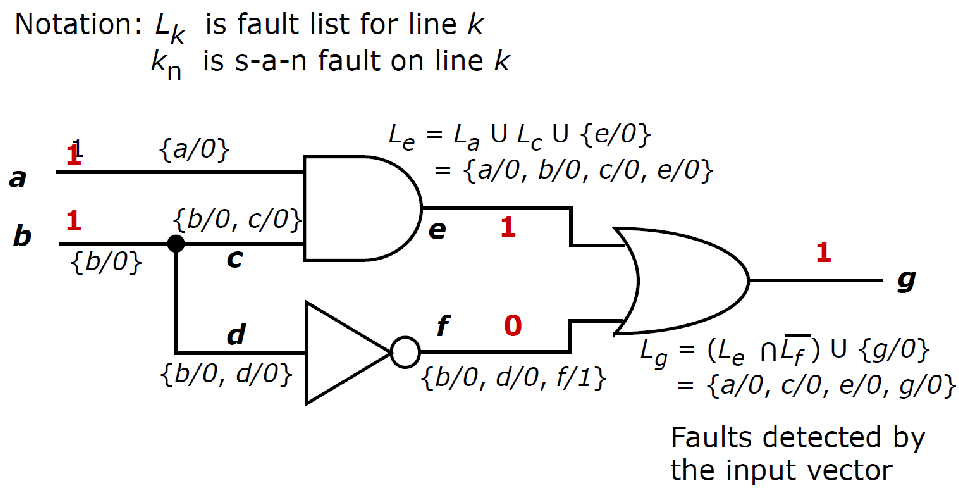

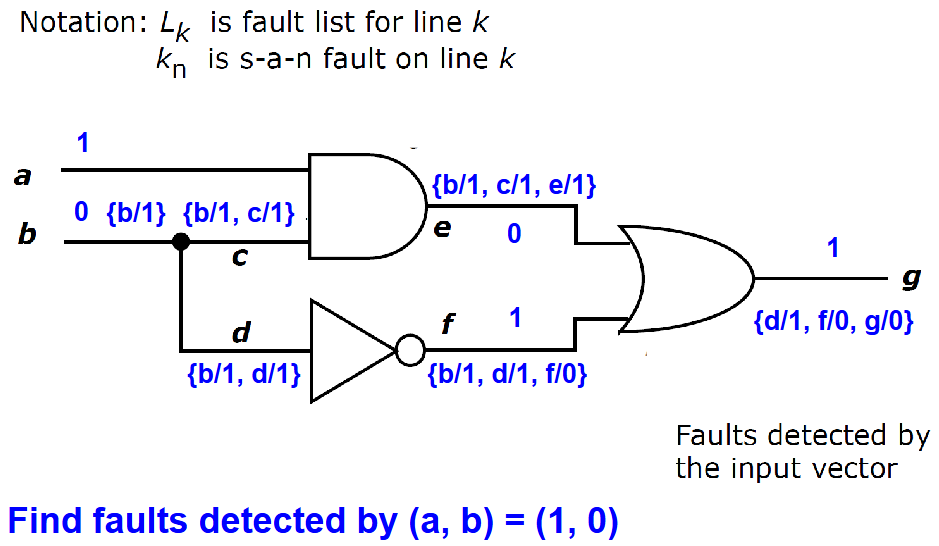

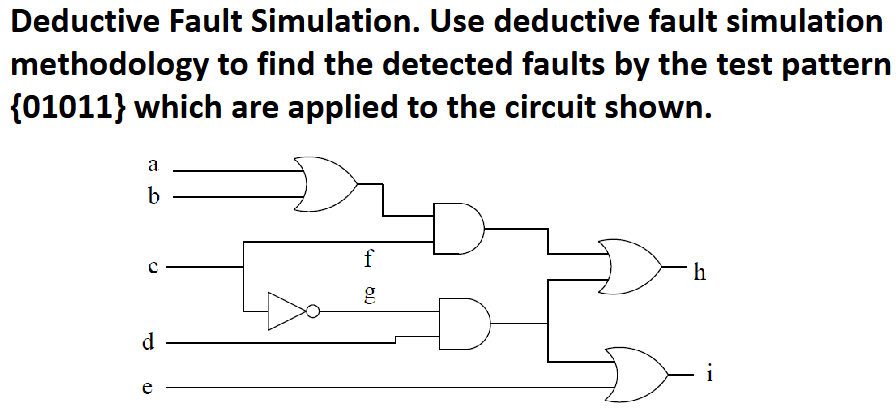

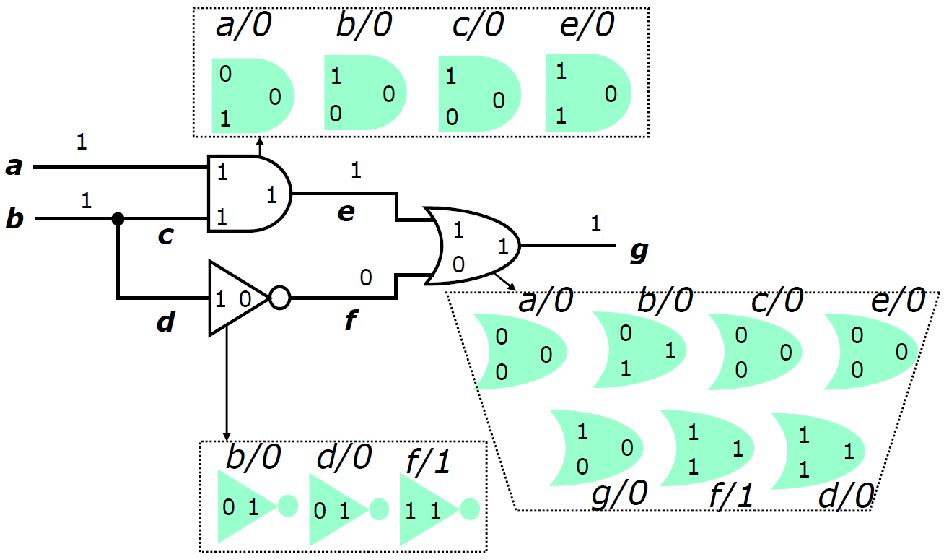

5.2.3 Deductive Fault Simulation(演绎故障仿真)

仅模拟无故障逻辑电路的运行行为,每个测试向量仅需单次遍历处理。各故障电路中的所有信号值,均依据无故障电路数值与电路结构推导得出。针对每个测试向量,按照从输入到输出的层级顺序(适用于组合逻辑电路),对所有线路执行推导运算。

故障列表

- 所有 在当前逻辑状态下 能导致 A 的信号值与无故障值不同 的故障名称或索引。

- 通常针对固定型故障(Stuck-at Faults),如 A stuck-at-0 (SA0) 或 A stuck-at-1 (SA1)

。

故障列表需要从原始输入 (PIs)端逐级传递至最终输出端 (POs),每条信号线都会生成专属故障列表,并在电路逻辑状态发生任何变化时,按需完成更新

故障列表发生变动时,即触发列表事件。

Example 1:

Example 2:

Practice:

5.2.4 Concurrent Fault Simulation(并发故障仿真)

对无故障电路,以及故障电路中信号状态与无故障电路存在差异的部分电路,开展事件驱动仿真。

为每个门电路单独建立列表,存放该门电路在所有存在差异的故障电路中的副本;列表元素包含故障编号、门电路输入输出值,以及内部状态(如有)。

所有无故障及故障电路的事件均被隐式模拟。比其他方法更快, 但占用内存最多。

Example 2:

Practice 1:

Practice 2:

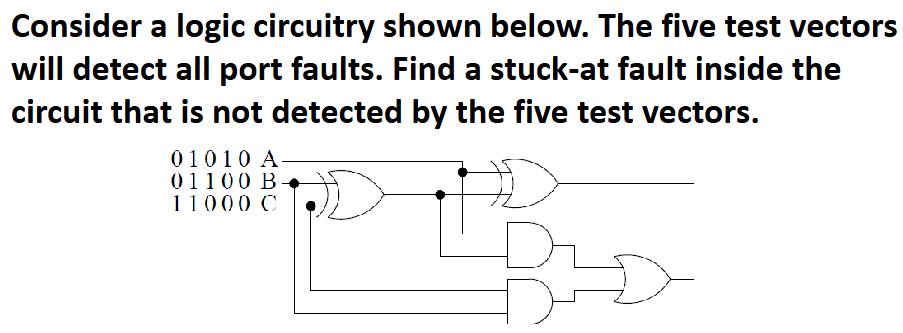

5.3 Functional Test and Structural Test(功能测试与结构测试)

测试向量(生成后的) 是用于数字系统的流片后测试。由于数字系统的复杂性、必要测试的规模以及测试质量因数等原因,测试向矗生成采用的是自动方法,该过程被称为自动测试向量生成 (Automatic Test Pattern Generation, ATPG),也简称为测试生成。

能测试就是为电路输入输出组合生成完整的测试集。129 个输入需要

结构测试只需要 64 位切片,每个切片包含 27 个故障,最多只需要测试

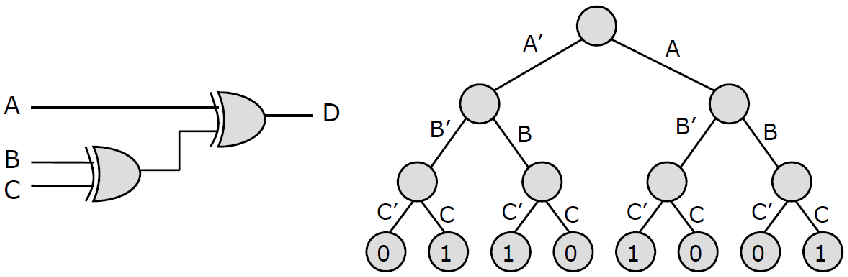

5.3.1 Circuit and Binary Decision Tree(电路与二元决策树)

所有自动测试向量生成程序都需要一种数据结构,用于描述测试码的搜索空间 —— 二元决策树。

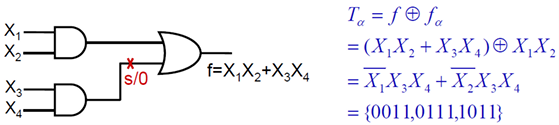

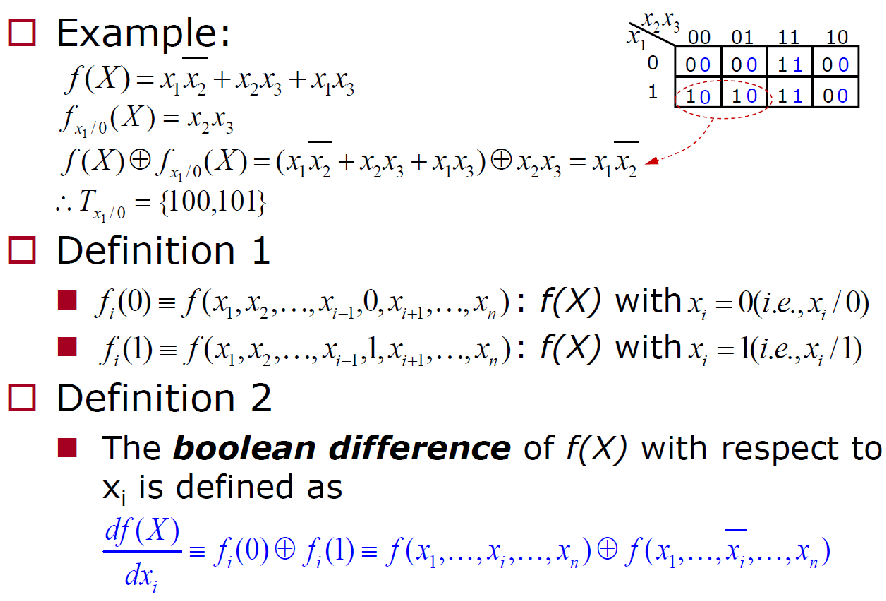

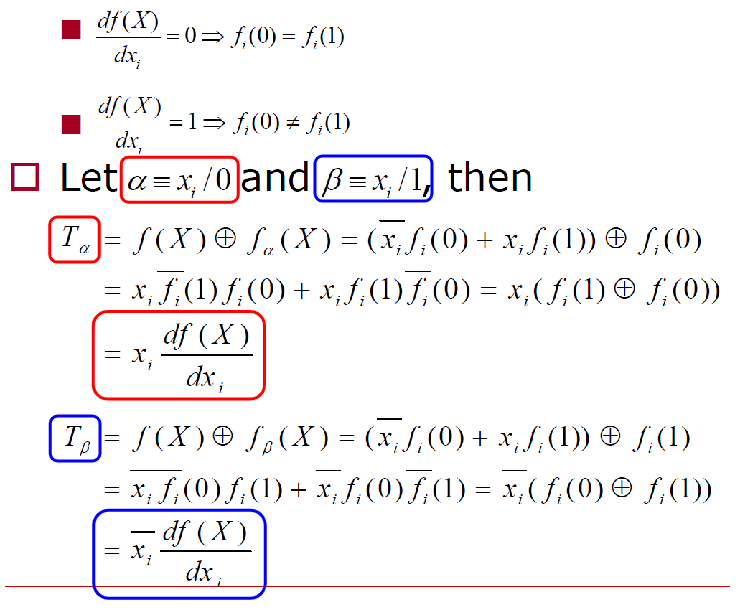

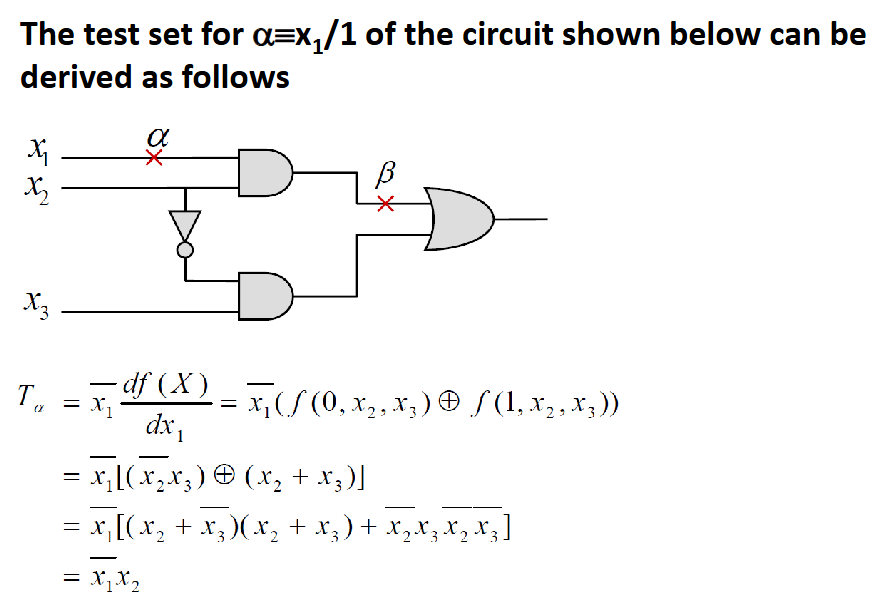

5.3.2 Boolean Difference(布尔差分)

布尔差分的目的是发现用于测试的输入向量。正常电路与故障电路的异或运算就是该布尔差分的方程, 针对该给定故障的测试就是使布尔差分为 1 的输入向量。

-

香农展开定理:

其实就是把复杂逻辑拆分成可计算的子问题

任意布尔函数

公式拆解:

-

-

- 公式的逻辑:原函数的结果,完全等于

-

-

布尔差分

-

无故障函数

-

故障函数

-

测试集公式

异或运算的特性是

两个输入不同时,输出为1。这个公式的含义是:当一个输入

-

Example:

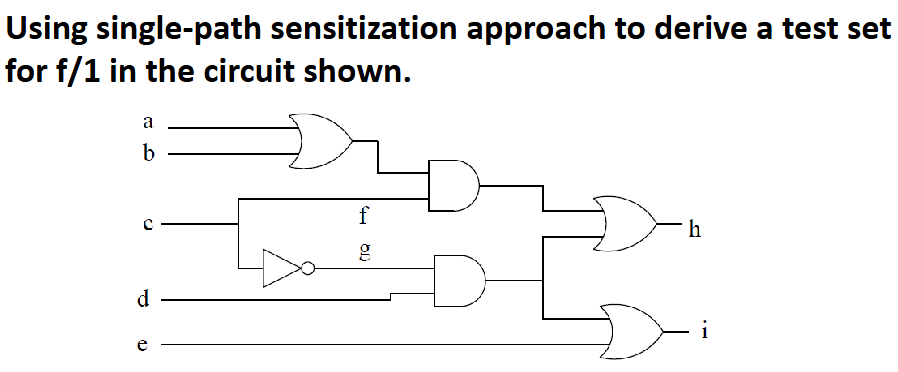

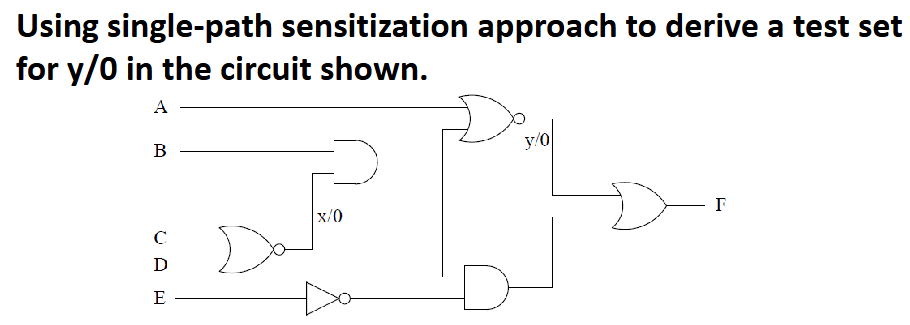

5.3.3 单路径敏化

我们已经知道,一个有效的测试向量必须满足两个核心条件:

- 故障激活:让故障点在正常电路和故障电路中的值产生差异,生成一个 “错误信号”;

- 故障传播:把这个错误信号一路传到芯片的主输出端,让我们能观测到故障带来的差异。

5.3.3.1 定义

(1) Fault activation(故障激活)

我们先明确基础符号:

- 正常电路中,线路

- 线路

- 主输出(Primary Output, PO):芯片可直接观测的输出端口

如果一个测试向量

举个例子:如果故障是a/1(a点永远固定为1,s/1故障),那我们需要让正常电路中a=0,这样正常状态a=0、故障状态a=1,成功激活故障。

(2) Fault Propagation(故障传播)

如果故障点的错误信号,能沿着某条路径传递到主输出z,让主输出的正常与故障值也出现差异 (

(3) 敏化线与敏化路径

- 敏化线:如果一条线路的信号值,会因为故障的发生而变化,这条线就被测试向量对故障敏化了。

- 敏化路径:由多条敏化线组成的、从故障点到主输出的完整路径,就是敏化路径。

- 单路径敏化:只选择一条从故障点到输出的路径,将其设置为敏化路径,让故障沿着这一条路径传递到输出端,这就是单路径敏化法的核心思想。

5.3.3.2 单路径敏化的步骤

单路径敏化法有一套固定的执行流程,严格按照这三步操作,就能为简单组合电路生成有效的测试向量。

Step 1: 故障激活 (Fault Activation/Excitation)

核心目标:让故障点产生错误信号,也就是让正常电路的故障点值,和故障状态的值完全相反。

固定执行规则:

- 对于

s/1故障(线路永远固定为1):正常电路中给这条线路赋值0,制造 正常=0、故障=1 的差异; - 对于

s/0故障(线路永远固定为0):正常电路中给这条线路赋值1,制造 正常=1、故障=0 的差异。

Step 2: 故障传播 (Fault Propagation)

核心目标:选择一条从故障点到主输出的路径,为路径上所有门电路的"非路径输入"赋合适的值,让故障的错误信号能沿着这条路径,一级一级传递到输出端。不能让门电路屏蔽错误信号,必须让门电路的输出完全由带错误的路径输入决定。不同门电路的传播规则如下:

| 门电路类型 | 错误信号通过的条件(非路径输入赋值) |

|---|---|

| 与门/与非门 | 非路径输入必须赋值1(与门只要有一个输入为1,输出就由另一个输入决定,错误信号可正常传递) |

| 或门/或非门 | 非路径输入必须赋值0(或门只要有一个输入为0,输出就由另一个输入决定,错误信号可正常传递) |

| 非门 | 无额外输入,直接反向传递错误信号 |

例如:错误信号要通过一个 2 输入与门,另一个输入必须设为1。如果设为0,不管错误输入是0还是1,输出永远是0,错误就被完全屏蔽了。

Step 3: 线值确认(Line Justification)

核心目标:从前面两步设置的内部线路值,反向推导到电路的主输入,为所有主输入赋确定的值,同时检查是否存在赋值矛盾。

执行逻辑:从故障点、传播路径上的赋值出发,一级一级向前推导,给每个门的输入赋值,直到所有主输入都有确定的值。

- 如果推导过程中,出现同一个输入既要赋

0、又要赋1的情况,说明这条传播路径走不通,需要回到step 2,换一条路径重新执行; - 如果推导完成后没有矛盾,得到的主输入组合,就是这个故障的有效测试向量。

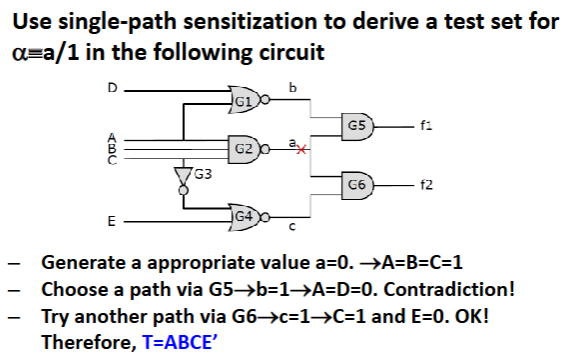

Example:

Step 1:故障激活

故障为a/1(s/1故障),根据规则,正常电路中需要给 a 赋值 0。

G2 是 3 输入或非门,或非门输出 0 的条件是所有输入全为 1,因此得到:A=1、B=1、C=1。

Step 2:故障传播,选择路径

故障点 a 有两条到主输出的路径可选:

- 路径 1:

a → G5 → f1 - 路径 2:

a → G6 → f2

(1) 先试路径 1:a→G5→f1

G5 是与门,要让 a 的错误信号传递到 f1,根据规则,与门的另一个输入 b 必须赋值 1。

b 是 G1 或非门的输出,或非门输出 1 的条件是至少有一个输入为 0,G1 的输入是 D 和 A,因此需要A=0或D=0。

但步骤 1 中我们已经确定A=1,如果强行让A=0就会出现赋值矛盾,因此这条路径走不通,需要换路径。

(2) 再试路径 2:a→G6→f2

G6 是与门,要让 a 的错误信号传递到 f2,与门的另一个输入 c 必须赋值 1。

c 是 G4 或非门的输出,或非门输出 1 的条件是至少有一个输入为 0。

G4 的输入是 E 和 G3 的输出,G3 是非门,输入A=1,因此 G3 的输出固定为 0 —— G4 已经有一个输入为 0,因此不管 E 取何值,G4 的输出 c 一定是 1,完美满足我们的要求,没有任何赋值矛盾。

这里我们给 E 赋值0,完成路径设置。

Step 3:线值确认,得到测试向量

整理所有主输入的赋值:

A=1、B=1、C=1(来自故障激活)E=0(来自故障传播)D无赋值要求,可赋0(不影响测试结果)

最终得到有效测试向量:A=1, B=1, C=1, E=0,对应布尔表达式T=ABCE'。

Practice 1:

Practice 1:

5.4 时序电路测试

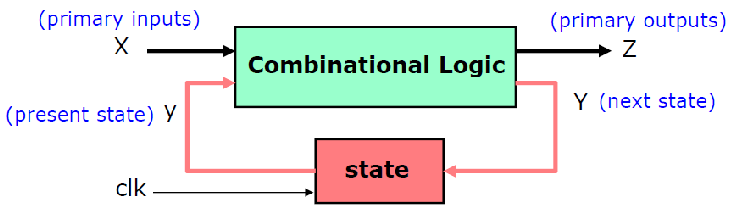

同步时序电路的经典模型是Huffman模型,它由两部分组成:

- 组合逻辑模块:负责逻辑运算,产生输出和下一个状态的激励;

- 状态记忆模块:由触发器(Flip-Flop)组成,保存电路的当前状态。

它的核心特性是:电路的输出不仅和当前的输入有关,还和电路当前的状态有关;而当前的状态,又由之前的输入和状态共同决定。简单来说,时序电路是有 “记忆” 的,它的行为是一个随时间变化的序列,而不是组合电路那样的"输入 - 输出"对应关系。

时序电路 ATPG 方法主要有两种:

- 时间帧展开法(Time-frame expansion methods)

- 基于仿真的方法(Simulation-based methods)

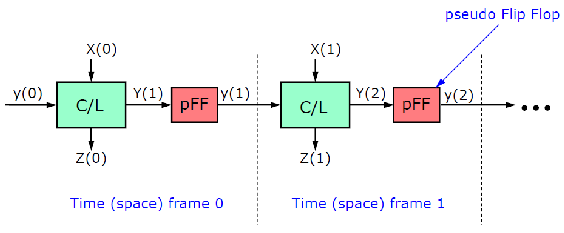

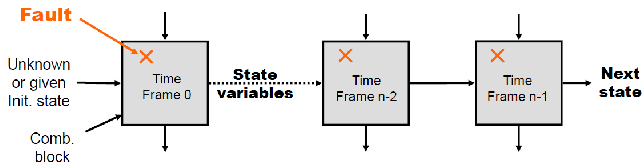

5.4.1 Time-Frame Expansion(时间帧拓展)

时间帧展开法的核心思想,是把复杂的时序问题,转换成我们熟悉的组合问题。

我们可以把同步时序电路的每个时钟周期,拆成一个独立的时间帧。

- 每个时间帧里,只包含当前时钟周期内的组合逻辑;

- 帧与帧之间,用伪触发器(pseudo Flip-Flop, pFF) 连接,它的作用是把前一个周期的电路状态,传递到下一个周期的时间帧里。

当我们把时序电路按时钟周期展开后,原本的时序电路,就变成了一个纯组合逻辑构成的迭代逻辑阵列(Iterative Logic Array, ILA)。原本带记忆、随时间变化的时序电路,被我们转换成了一个无记忆的纯组合逻辑电路。

5.4.2 时间帧展开法的原理

对于同步时序电路 (也就是有限状态机 FSM),我们可以通过展开 Huffman 模型,把它转换成迭代逻辑阵列 ILA;然后对这个纯组合的 ILA,应用路径敏化算法,生成对应的测试序列;最后把每个时间帧的输入按顺序组合,就是时序电路的测试序列。

这里有一个和组合电路的核心区别:时序电路里的一个固定型故障 (比如 a/1,线路永远固定为 1),是永久存在于电路中的。所以在我们展开的每一个时间帧里,这个故障都会存在,相当于在组合阵列里出现了多个相同的故障,也就是多故障场景,这是时序电路测试和组合电路最核心的差异之一。

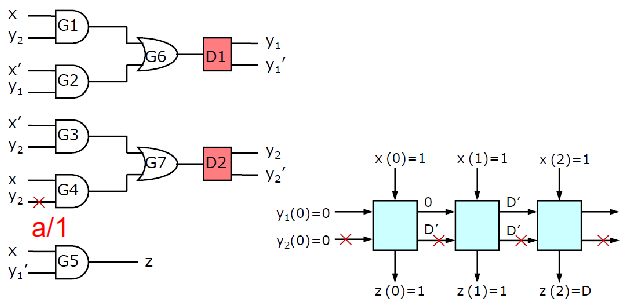

Example:

推导故障a/1的测试序列:

我们的目标是:找到一组连续的x输入,让正常电路和故障电路的z输出出现可观测的差异。

Solution:

Step 1:初始状态与故障激活(

初始状态:

,

- 故障激活要求:

a/1故障,需要让正常电路的a=0,故障电路的a=1,产生信号差异。a=0、故障a=1,故障激活成功! - 故障传播要求:故障在

G4的输入,G4是与门,要让故障差异传递到G4的输出,另一个输入x必须设为1(与门的非路径输入设为 1,输出才会由故障输入决定)。因此x(0)=1。

此时正常电路和故障电路的差异已经出现:

-

正常电路:

G4输入x=1、a=0G3输入x'=0、G7输出0D2的 D 端 = 0 -

故障电路:

G4输入x=1、a=1G3输出 0;G7输出 1D2的 D 端 = 1

故障的差异已经成功传递到了下一个周期的状态

中:

周期正常电路

,故障电路

。

Step 2:故障差异的状态传递(

我们需要把

的差异,进一步传递到

的状态中,为后续传递到主输出做准备。

周期输入x(1)=1,此时:

-

正常电路:

G1输入x=1、G2输入x'=0、G6输出 0D1的 D 端 = 0 -

故障电路:

G1输入x=1、G2输出 0;G6输出 1 →D1的 D 端 = 1

现在,故障差异已经传递到了

的状态中:t_2周期正常电路

,故障电路

Step 3:故障差异传播到主输出(

主输出z由G5或门决定,输入是x'和

(

的反相)。要让

的差异传递到z,x'必须设为 0(或门的非路径输入设为 0,输出才会由故障输入决定),也就是x(2)=1。

此时正常和故障电路的输出差异:

- 正常电路:

y1=0→x'=0→G5输出0|1=1 - 故障电路:

y1=1→x'=0→G5输出0|0=0

正常电路输出z=1,故障电路输出z=0,差异成功传递到主输出,我们可以通过观测z的值判断故障是否存在。

最终测试序列:

把三个周期的输入按顺序组合,得到有效测试序列:x(0)=1、x(1)=1、x(2)=1,也就是序列111,和 PPT 的结果完全一致。

在时间帧展开的过程中,有两个明确的终止条件:

- 成功终止:如果主输出出现了正常和故障的差异(输出为

D或D'),说明我们找到了有效的测试序列,停止展开。- 失败终止:如果展开的帧数

超过了 (n是电路里触发器的数量),说明这个故障是冗余故障,无法被检测到,停止展开。

这个规则的原理是:n个触发器最多有

个状态, 是所有状态转移的最大数量,超过这个数还没找到测试序列,说明故障永远无法传播到输出。

Practice:

6 可测性设计(Design for Testability, DFT)

如果存在一个明确规定的程序来暴露一个故障,那么它是可测试的,且该程序利用现有技术能以合理成本实现。当针对某个故障集中的每一个故障都是可测试的时, 称该电路相对于该故障集是可测试的。

可测试性设计(DFT) 是指那些使测试生成和测试应用具有成本效益的设计技术。

电子系统包含三类组件: (a) 数字逻辑、 (b) 存储模块, 以及 © 模拟或混合信号电路。

DFT 的核心目标,是提升电路的两大核心可测性指标:

- 可控性(Controllability):衡量控制电路中某一条线路电平状态的难易程度

- 可观测性(Observability):衡量在电路主输出(Primary Output, PO)处观测到某一条线路状态的难易程度

同时,DFT 的引入会带来多维度的设计成本,主要包括:面积/良率损耗、引脚资源占用、电路性能退化、设计周期延长。

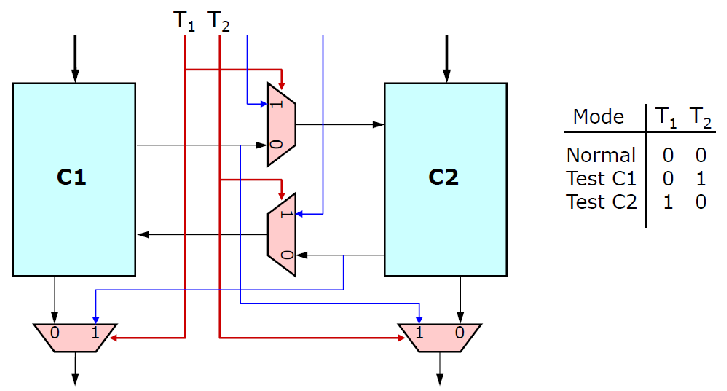

6.1 Ad Hoc DFT(临时可测试性设计)

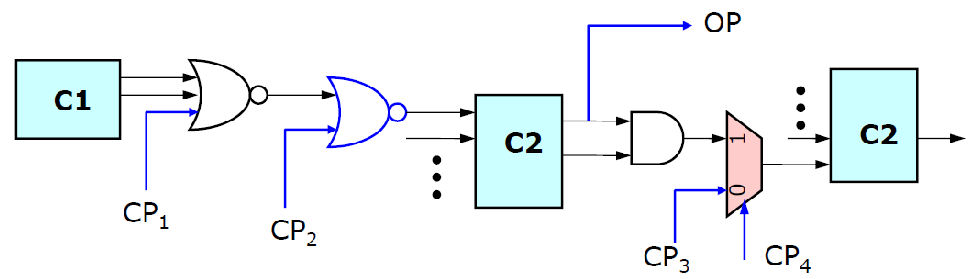

将大型电路划分为更小的子电路,通过多路选择器(MUX)扫描链降低测试生成成本:

插入测试点增强电路的可控性与可观测性,测试点分为控制点(Control Point, CP)和观测点(Observation Point, OP)两类:

临时 DFT 设计准则:

- 设计易于初始化的电路

- 增设逻辑电路以切断全局反馈回路

- 将大型计数器拆分为多个小型计数器

- 避免使用冗余逻辑

- 模拟电路与数字电路进行物理隔离

- 避免使用异步逻辑

- 考虑测试设备要求(引脚限制等)

Ad Hoc DFT 的局限性:

- 大量的 I/O 引脚;

- 可以通过添加多路复用器来缓解;

- 测试时间过长;

6.2 扫描设计(Scan Design)

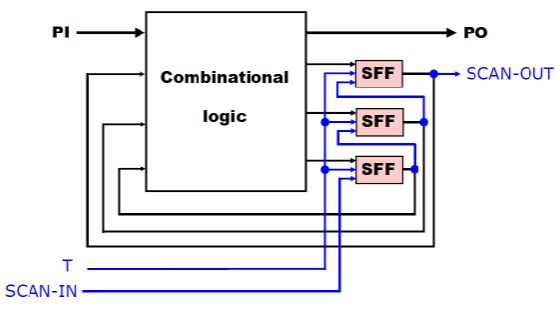

扫描设计是现代 IC 设计中最主流的结构化 DFT 技术,其主要作用在于:

- 实现高效的电路划分

- 为电路内部的状态变量提供测试所需的完全可控性和可观测性

- 将复杂的时序电路测试问题,转化为简单的组合电路测试问题

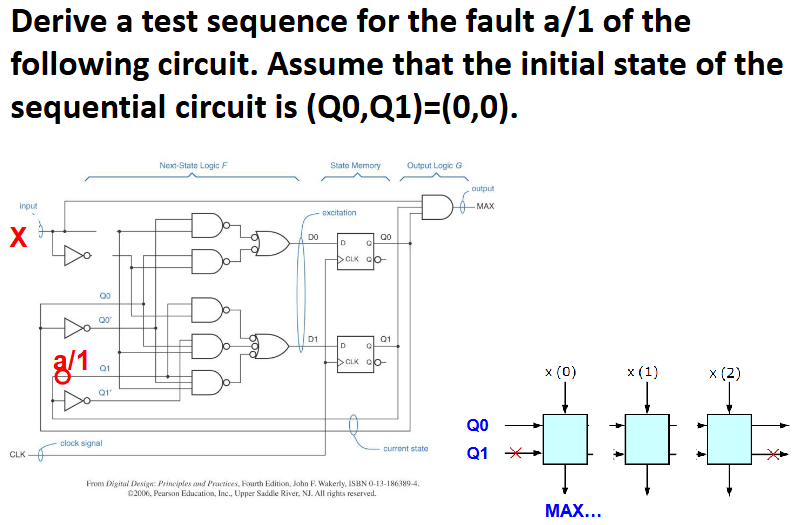

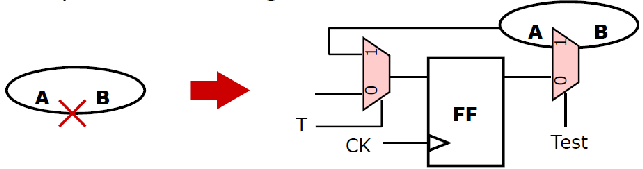

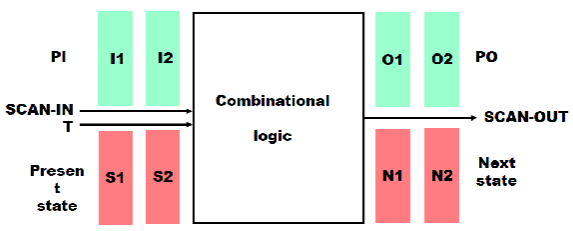

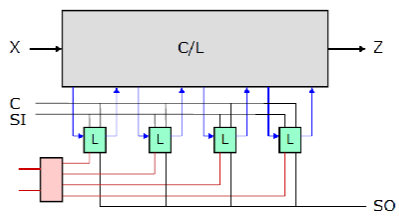

我们考虑一种时序电路:

如上图,为实现扫描功能,需要在原始时序电路中添加硬件:

-

测试模式引脚(T)

-

扫描输入引脚(SI)

-

扫描输出引脚(SO)

-

每个触发器(FF)的前端添加一个二选一多路选择器(MUX),形成扫描触发器(SFF)

所有 SFF 串联形成完整的扫描链,实现状态的串行移入与移出。

6.2.1 扫描设计的规则与违例修正(Scan Test Generation and Design Rules)

扫描测试生成流程:

- 使用组合 ATPG 工具,为组合逻辑中所有可测试故障生成测试向量

- 添加移位寄存器测试,将 ATPG 生成的组合测试转换为扫描序列,用于芯片量产测试

扫描设计规则:

- 所有状态变量必须仅使用带时钟的 D 型触发器

- 至少有一个主输入(PI)引脚可用于测试,可用引脚越多越优

- 所有时钟必须从主输入(PI)端控制

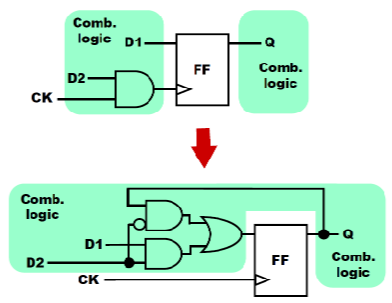

- 时钟信号不得直接馈入触发器的数据输入端

6.2.2 扫描设计规则违例修正(Correcting a Rule Violation)

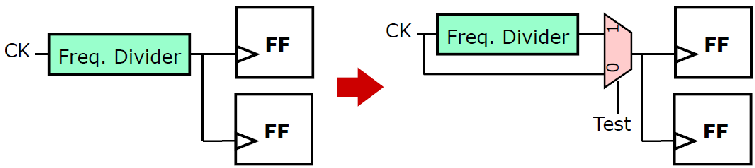

针对"时钟未从 PI 控制"的违例,重构时钟路径,确保所有时钟必须由 PIs 控制。

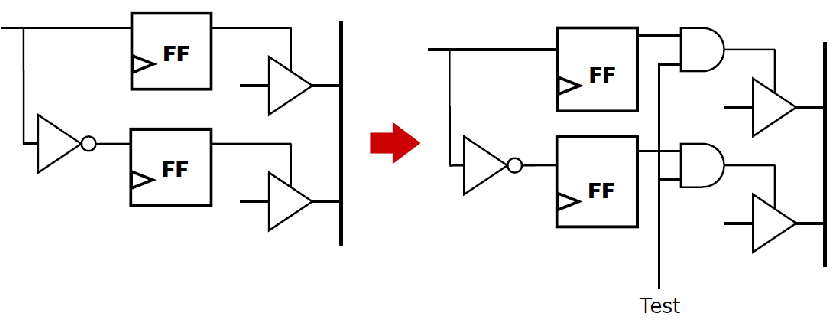

通过添加扫描 FF 和 MUX,在测试模式下断开反馈环路,提升电路可测试性;

针对分频生成的衍生时钟,使用 MUX 在测试模式下旁路分频级,确保时钟直接受控于主输入:

通过与门逻辑,确保测试期间总线驱动器不会被正常逻辑激活,避免测试过程中出现总线冲突:

6.2.3 扫描测试的流程(Scan Test Procedure)

- 切换到移位寄存器模式,通过移入 1 和 0 的交替序列(如 00110),检查移位寄存器的基础工作状态(扫描链功能测试)

- 初始化移位寄存器,串行加载第一个测试图案到扫描链中

- 切回电路正常工作模式,施加测试图案,捕获电路的响应结果

- 再次切换到移位寄存器模式,串行移出捕获的最终状态,同时为下一次测试设置起始状态;循环执行步骤 3,完成所有测试向量的验证

6.2.4 测试向量合并(Combining Test Vectors)与测试序列长度计算

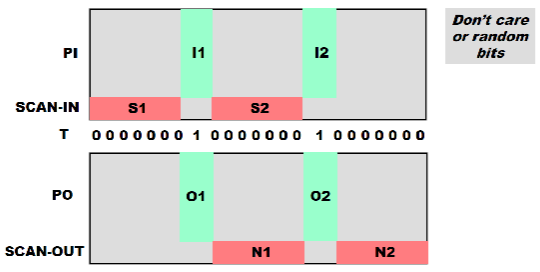

测试向量的合并方法就是将主输入(PI)、扫描输入(SCAN-IN)、测试模式(T)的激励向量合并为统一的测试序列,同时将主输出(PO)、扫描输出(SCAN-OUT)的响应结果合并观测。

扫描测试序列长度的核心计算公式:

其中:

6.2.5 Testing Scan Register(测试扫描寄存器)

扫描寄存器必须在施加扫描测试序列之前完成测试

- 在扫描模式(测试控制信号 = 0)下,长度为

00110011...,可在所有触发器中产生00、01、11、10四种跳变,并在扫描输出端观测结果 - 示例:2000 个扫描触发器、500 个组合逻辑向量,总扫描测试时长约

- 采用多组扫描寄存器可缩短测试时长

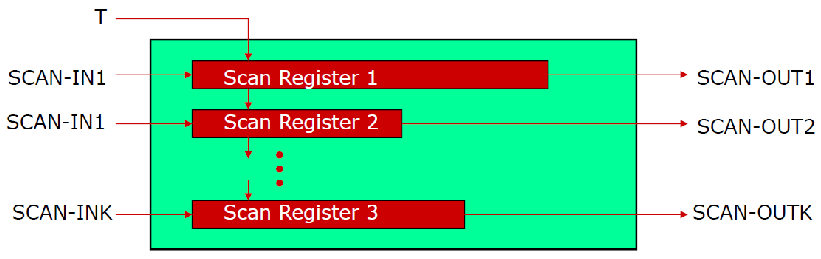

6.2.6 多扫描寄存器(Multiple Scan Registers)

-

扫描触发器可分布到任意数量的移位寄存器中,每个扫描链都有独立的 SCAN-IN 和 SCAN-OUT 引脚

-

测试序列长度由最长的扫描移位寄存器决定

-

整个设计仅需一个测试控制(TC)引脚即可完成多链控制。

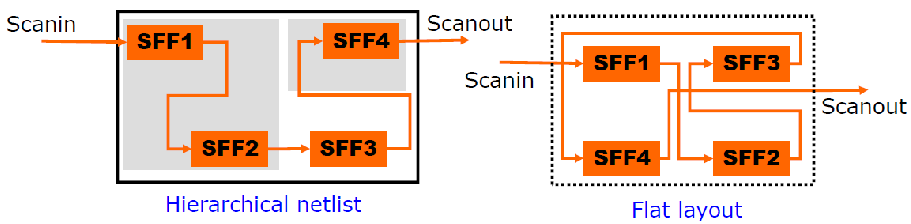

6.2.7 层次化扫描(Hierarchical Scan)

扫描触发器先在子网络内完成成链,再将子网络级联形成顶层扫描链。

优势:

- 在于支持网表中自动插入扫描

- 保留电路原始层次结构,便于设计调试与工程变更

缺点:

- 芯片布局布线非最优。

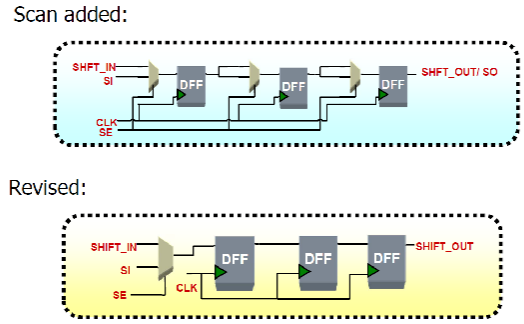

6.2.8 Shift Registers

为基础移位寄存器添加扫描输入(SI)、扫描使能(SE)、同步时钟(CLK),完成扫描功能的适配。

6.2.9 随机存取扫描(Random Access Scan)

随机存取扫描的原理就是使用可寻址锁存器,通过多路复用的地址选择,实现对任意触发器的随机存取,无需串行移位遍历全链。

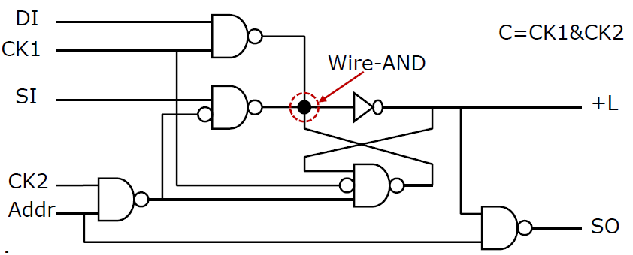

随机存取扫描单元的硬件结构如下:

优势:

- 测试速度快,对电路正常工作路径影响极小;

- 支持随机存取,测试效率高;

- 可在电路正常工作模式下实时 “监控” 节点状态

缺点:

- 硬件开销大,需要额外增加大量引脚

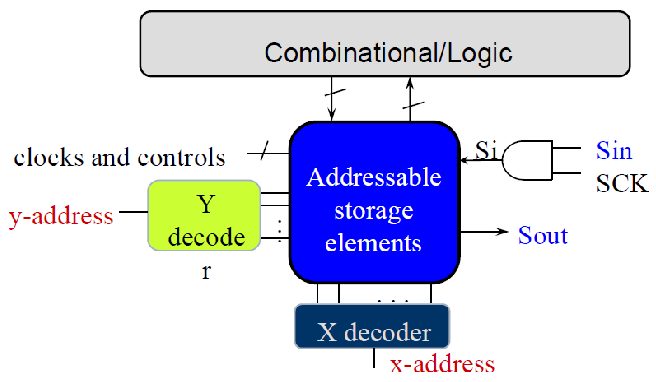

随机存取扫描的整体架构:

包含 X/Y 地址译码模块、可寻址存储单元、扫描输入/输出、扫描时钟等模块;正常工作时,存储单元工作在并行加载模式;扫描写入时,通过地址寻址对应单元,将测试数据施加到扫描输入端。

随机存取扫描的标准化测试流程:

- 为所有测试点设置测试输入

- 施加主复位信号,初始化所有存储单元

- 设置扫描输入地址和数据,施加扫描时钟完成单单元写入

- 重复步骤 3,直到所有内部测试输入完成扫描写入

- 施加一个正常工作时钟,捕获电路响应

- 检查电路输出点的状态

- 施加对应的 X-Y 寻址信号,逐单元读取所有存储单元的扫描输出状态

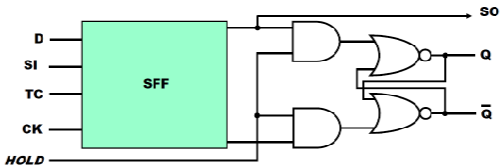

6.2.10 扫描保持触发器(Scan-Hold FFs, SHFFs)

扫描保持触发器(Scan-Hold FFs, SHFFs)的特性为,当控制端 HOLD=0 时,Q 与 Q’输出将固定在触发器的前一状态;核心应用场景为降低扫描移位过程中的电路功耗。

多时钟设计的扫描挑战:

- 不同时钟域之间可能出现时钟偏斜(Clock Skew),导致扫描移位出错;

优化方案包括:

- 扫描链排序时,将相同时钟域的所有触发器分为一组,最大限度减少时钟偏斜的发生位置;

- 在跨扫描/时钟域的边界,插入锁存锁存器(lockup latch),彻底避免时钟偏斜带来的时序违例。

扫描设计的工程问题:

-

扫描链排序:

- 核心目标是避免移位过程中的时钟偏斜、最小化布线开销,通常基于布局信息确定最优排序

-

扫描链平衡:

-

核心目标是最小化总测试时间;

-

总扫描周期计算公式为:

扫描链的数量通常受芯片封装(可用引脚数量)和测试机(通道数与存储深度)限制

-

6.2.11部分扫描设计(Partial Scan)

部分扫描设计是全扫描设计的轻量化方案,其思路就是选择触发器的一个子集进行扫描改造,而非设计中的全部触发器。

相比全扫描,其优势为主要为更低的面积和速度开销、更宽松的设计规则。

给出了两种实现方法:

- 周期中断技术(Cycle-breaking technique)

- 通过选择扫描触发器,简化时序 ATPG 的复杂度

- 时序驱动的部分扫描

- 可同时实现面积、时序和可测试性的协同优化

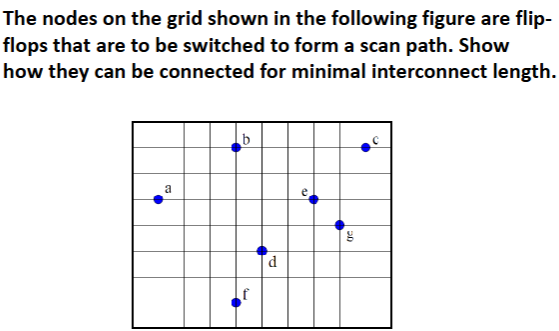

Practice 1

网格节点上的触发器需组成扫描路径,需给出最优连接方式,实现最小互连长度(扫描链重排序优化)。

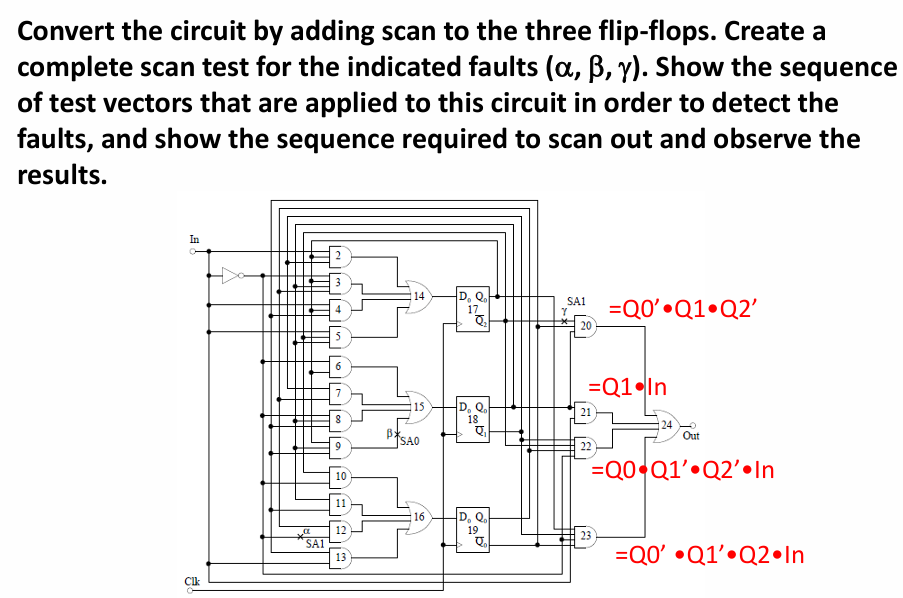

Practice 2

为包含 3 个触发器的时序电路添加完整扫描结构,为指定故障

6.2.12 综合征可测试设计(Syndrome-Testable Design)

综合征可测试设计是一种面向组合逻辑的可测性设计方法.

-

布尔函数

-

综合征(Syndrome):在数字电路测试中,指的是电路输出为 1 的总次数,占所有可能输入组合的比例(也叫 1 的概率或权重)。

-

综合征可测试性:一个电路是综合征可测试的,当且仅当对于任意故障

-

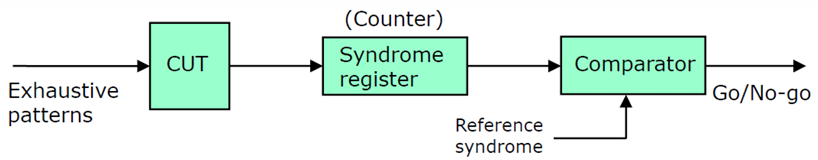

典型综合征测试架构:由计数器生成穷举测试图案、被测电路(CUT)、综合征寄存器、参考综合征存储、比较器组成,最终输出 Go/No-go 测试结果

-

基础逻辑门的综合征:

门电路类型 n 输入与门 ANDn n 输入或门 ORn n 输入异或门 XORn 非门 NOT 综合征值S

Example1:

考虑一个包含两个模块 f 和 g、且输入相互独立的电路:

| 输出门类型 | 或门(OR) | 与门(AND) | 异或门(XOR) | 与非门(NAND) | 或非门(NOR) |

|---|---|---|---|---|---|

| 综合征值

|

|

|

|

|

|

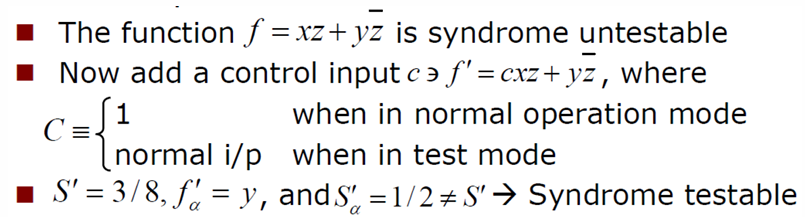

给出一个综合征不可测试的典型案例:函数

- 无故障综合征

- 当发生

可测试性定理:

-

单边函数(unate):逻辑函数在变量

-

例如:

任何二级无冗余电路,都可以通过为与门添加控制输入,改造为综合征可测试电路。

Example 2:

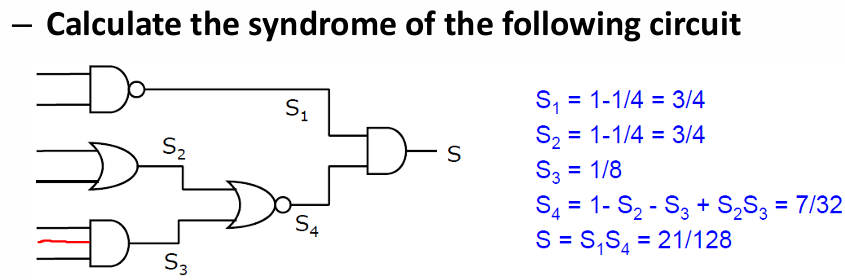

Practice:

Calculate the syndrome of the following circuit using the syrdromes of logic gates.

6.3 内建自测试(Built-In Self-Test, BIST)

BIST 就是电路完成自我测试的能力。

BIST 的优势在于:

- 测试图案片上生成,大幅提升电路可控性

- 片上完成(压缩后的)响应评估,大幅提升电路可观测性

- 支持在线(并发)或离线测试两种模式

- 可在电路额定工作速度下运行测试,测试场景更真实、测试时间更短,更易实现延迟故障测试

- 大幅简化外部测试设备,甚至可完全消除对昂贵 ATE 的依赖

- 对工程变更的适配性极强

6.3.1 在线与离线 BIST

在线 BIST (On-line BIST):

- 并发(EDAC、NMR、完全自检检查器等):

- 编码或模块化冗余技术(容错)

- 即时纠正由临时或永久故障引起的错误

- 非并发(诊断程序):在系统处于空闲状态时执行

离线 BIST (Off-line BIST):

-

测试模式生成器(TPG):

- 伪随机生成器(PRPG):如线性反馈移位寄存器(LFSR)。

- 特征多项式:定义LFSR的反馈结构,决定生成序列的周期。

-

响应分析器:

- 签名分析(Signature Analysis):利用LFSR压缩响应,生成唯一签名。

- 其他技术:奇偶校验、1计数、转换计数等。

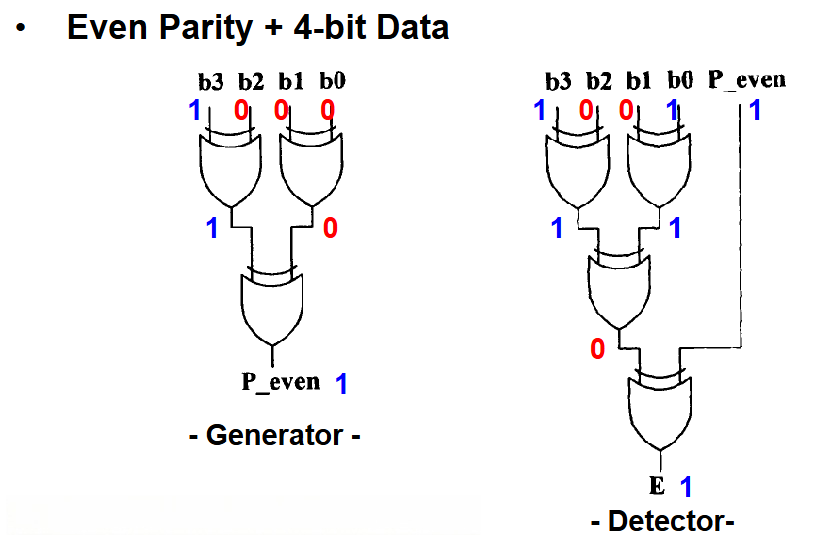

6.3.2 签名分析

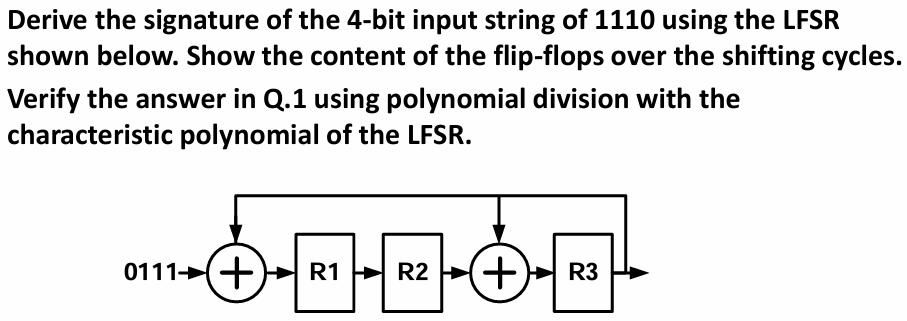

签名分析是一种基于循环冗余校验(CRC)概念的响应压缩技术,可通过 LFSR 在硬件中高效实现。

给出了线性函数的定义:

函数

其中

线性操作包括:

- 模 2 加、模 2 标量乘、延迟;

- 非线性操作包括 AND、OR、NAND、NOR 等。

6.3.3 线性反馈移位寄存器(Linear Feedback Shift Register, LFSR)

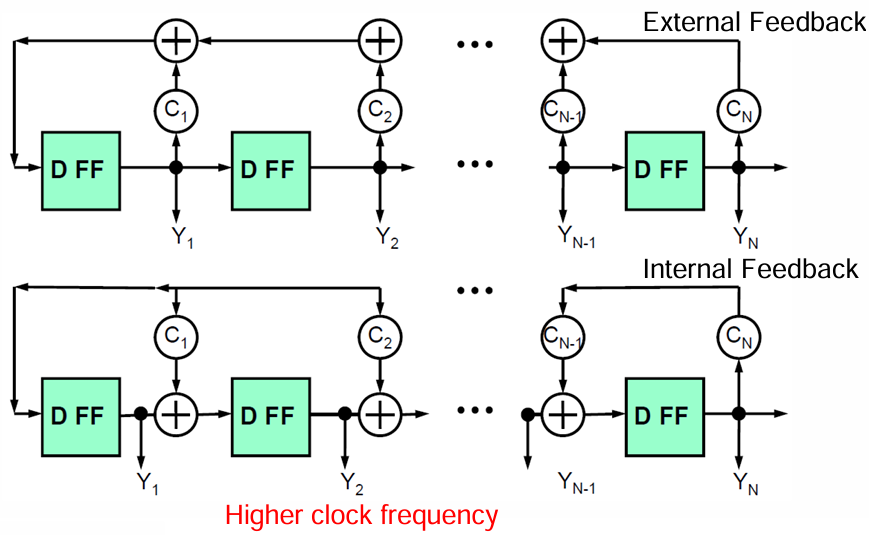

LFSR 有两种通用标准结构:

- 外部反馈 LFSR

- 内部反馈 LFSR:相比外部反馈结构,可实现更高的时钟频率

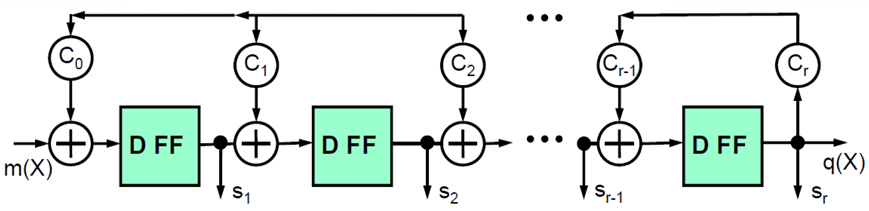

串行输入流可表示为多项式:

LFSR 的特征多项式定义为:

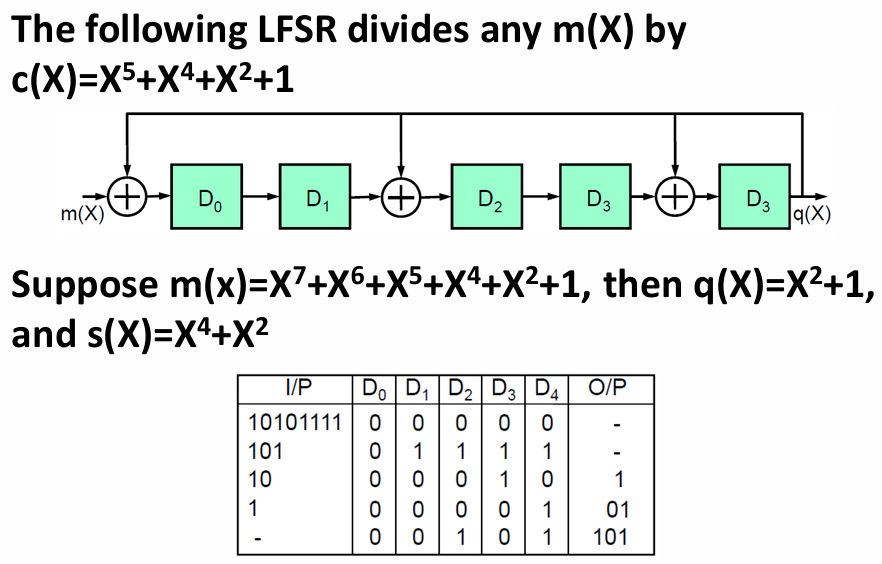

- 核心原理:当 LFSR 初始状态全 0 时,其本质是将输入多项式m(X)除以特征多项式c(X),即m(X)=q(X)⋅c(X)+s(X);其中商q(X)从移位寄存器输出串行出现,n+1 次移位后,余数s(X)(即签名)保留在移位寄存器中。

Example:

6.3.4 响应压缩Aliasing Probability

6.3.5 响应压缩

6.3.6 奇偶校验

6.3.7 One Counting

6.3.8 Transition Counting

6.3.9 伪随机模式生成器(Pseudorandom Pattern GeneratorPRPG)

逻辑内置自测试大多采用伪随机测试。这类测试通常比确定性测试长得多,但生成成本明显更低。

伪随机测试通过线性反馈移位寄存器或元胞自动机生成。

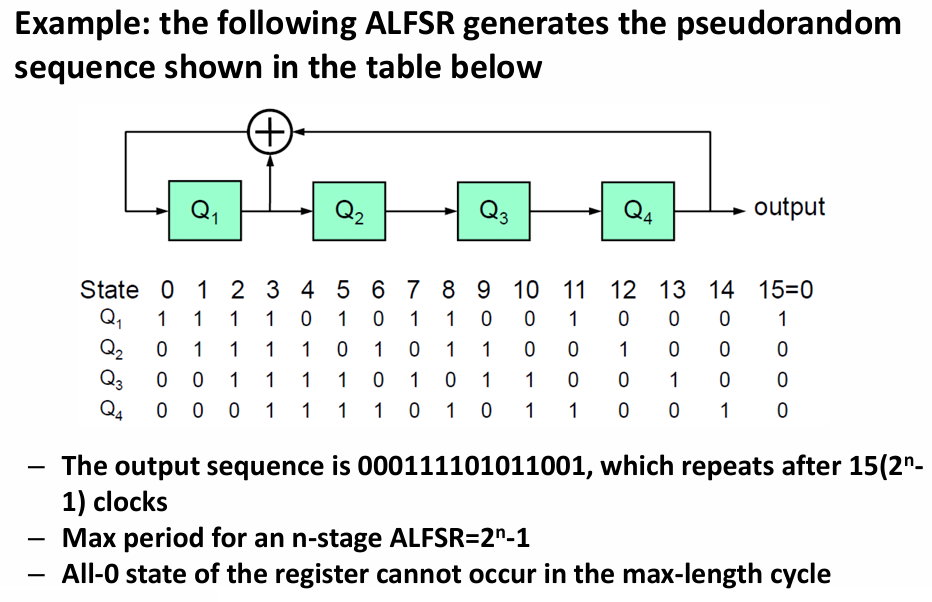

借助一种名为自主线性反馈移位寄存器(ALFSR)的简易电路实现。

定义:自主线性反馈移位寄存器是无外部输入的线性反馈移位寄存器。

难以通过伪随机测试检测到的故障,被称为随机图案抗性故障。

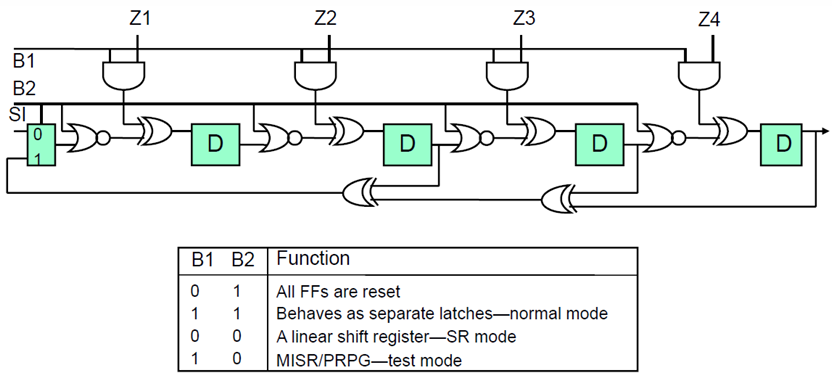

6.3.10 内建逻辑块观测器(BILBO)

BILBO 是多功能测试模块,可切换工作模式,作为测试生成器或签名分析器使用;其硬件由一行触发器和额外的门电路组成,实现移位和反馈操作;通过 B1、B2 两个控制位,可切换不同的工作模式。

Practice 1:

Practice 2: