1 内存管理(Memory Management)

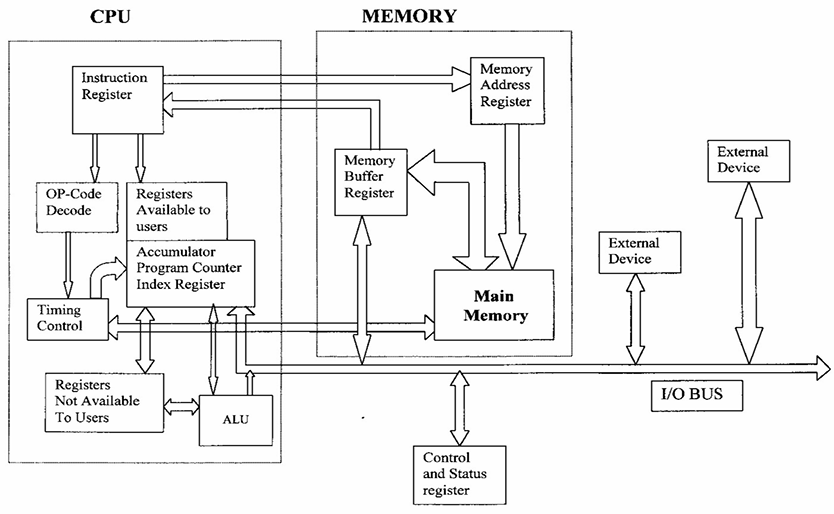

在冯诺依曼架构中,一个简单的计算机包含了以下四个组成部分:

- CPU

- Main Memory

- A Single System Bus

- I/O Devices

而现代计算机则更为复杂,组成部分如下:

- CPU

- Floating Point Processor

- **Accelerator **

- Cache

- **Main Memory (RAM) **

- **Secondary Memory (SSD Hard Disks,) **

- **Auxiliary Storage (External Hard Disks, USB Flash Drive, Cloud Drive) **

- I/O Devices (Terminals)

1.1 主存组织(Main Memory Organization)

主存是存储程序和数据的,并将其传输给 CPU 执行的区域。它是由多个存储单元(Cells/Locations)组成,每个单元拥有唯一的地址(Address),程序通过地址精准访问数据。

每个存储单元的结构分为两个部分:

- 数据位:真正存储指令、业务数据的部分,常见规格有8bit(1字节)、16bit、32bit等。

- 元位/标志位(Meta Bit/Tag/Valid/Flag Bit):附加在数据位旁的额外二进制位,不存储业务数据,相当于存储单元的"身份证",用来标识数据的属性和状态:

- 作用:

- 区分指令与数据:约定

0代表当前单元是CPU可执行指令,1代表是普通数据,避免CPU误把数据当指令执行。 - 区分数据类型:标记当前数据是整数还是浮点数,让CPU用正确的运算规则处理。

- 扩展作用:还可作为有效位标记数据是否有效、保护位标记读写权限等

- 区分指令与数据:约定

- 作用:

CPU 通过两个寄存器与内存交互:

-

MAR(Memory Address Register):地址寄存器。CPU 将要访问的内存地址放入 MAR,内存通过 MAR 解析目标位置。

-

MBR/MDR(Memory Buffer/Data Register):数据缓冲/寄存器。用于暂存 CPU 与内存之间交换的数据(读入时存数据,写出时存指令)。

CPU 读取内存数据(指令或数据)的步骤如下:

- CPU 将目标地址送入MAR。

- CPU 向内存发送读控制信号(Read Signal)。

- 经过一个存储周期(Memory Cycle) 后,内存将对应数据放入MBR。

- CPU从 MBR 中取出数据进行处理。

1.1.1 内存体(Memory Bank)

单内存模块的访问速度远低于CPU时钟速度,形成了经典的内存墙问题。

内存体技术将主存划分为多个独立可并行访问的存储模块(Bank),每个 Bank 拥有独立的地址译码、读写电路,可同时响应 CPU/I/O 的访存请求,从而大幅提升内存带宽与系统整体效率。

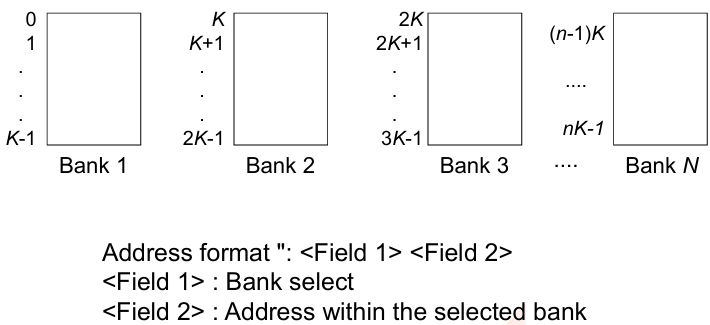

1.1.1.1 高位交织(High Order Interleave)

将连续的大块地址被分配到同一个Bank,相当于把内存分成多个独立的分区。 例如:Bank1存储地址

地址分为两个字段,格式为:<bank><addr>,高位用于选择Bank,低位用于Bank内寻址。这种方式支持多设备并行访问,当CPU和I/O设备使用不同Bank存储指令/数据时,可通过不同总线同时访问,互不干扰,提升系统并发性能。例如在流水线处理器中,将指令和操作数分别存放在不同Bank,实现取指令和读操作数的并行执行。

通俗来讲,我们可以把高位交织看成是把仓库分成多个独立大货架,每个货架放一类货物(指令或数据),不同工人(CPU和I/O)可同时去不同货架取货。

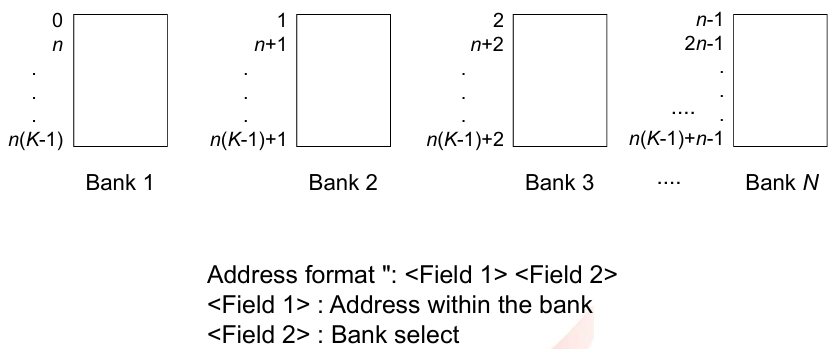

1.1.1.2 低位交织(Low Order Interleave)

与高位交织不同,其地址分配逻辑是连续的地址被交替分配到不同Bank,形成流水线式访存结构。 例如:10个Bank时,Bank1存储0,10,20,30...,Bank2存储1,11,21,31...。

同样的,地址还是分为两个字段,格式为:<addr><bank>,但变成低位用于选择Bank,高位用于Bank内寻址。这样可以实现连续访存流水线化,让内存有效访问速度匹配CPU时钟。CPU可在等待Bank1访存完成的同时,依次访问Bank2、Bank3…,等轮完所有Bank回到Bank1时,前一次访存已完成,可立即发起下一次访问,最终将内存访问速度提升至接近CPU速度。

将低位交织比作把仓库货物按顺序轮流放到多个货架,工人(CPU)可按顺序依次从不同货架取货,无需等待前一个货架取货完成,实现流水线取货。

Example:

CPU时钟为200MHz,内存访问周期为50ns,需要多少个Bank、采用何种交织方式,才能让内存访问速度匹配CPU?第1个Bank的地址是什么?

Solution:

-

计算CPU周期

CPU周期 =

-

计算Bank数

采用低位交织,Bank数 = $\frac { 内存周期 } { CPU周期 } $=

-

第1个Bank的地址

低位交织中,第1个Bank的地址为

0, 10, 20, 30...(步长为Bank数10)

1.1.2 内存管理单元(Memory Management Unit, MMU)

MMU是操作系统的核心组件,负责监管所有存储设备之间的信息流动。其的要求是在满足系统性能要求的前提下,最小化每比特存储的成本(cost per bit of storage)。

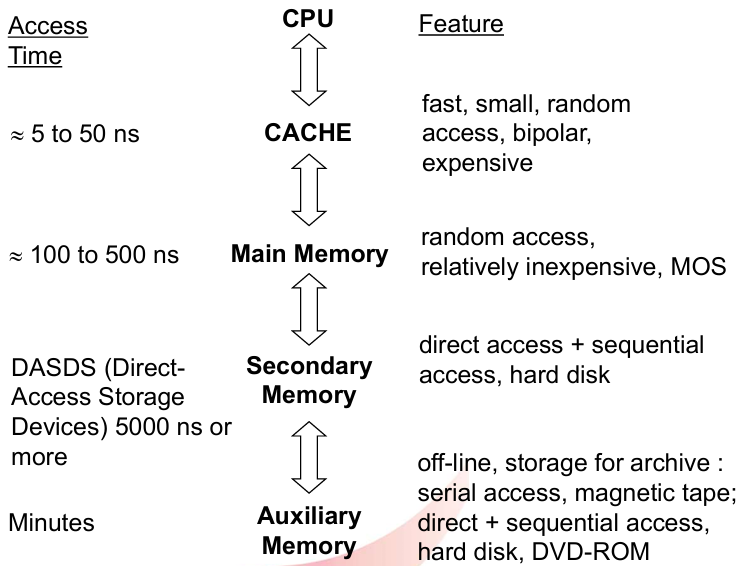

通过 分层存储结构(Hierarchical Memory) 实现,由多级不同速度、不同成本的存储器组成金字塔结构,越靠近 CPU 的层级速度越快、容量越小、成本越高;越远离 CPU 的层级速度越慢、容量越大、成本越低。主要功能如下:

- 调整层次中各存储器的访问频率,最大化高速存储的利用率

- 提供高效的层级间数据传输机制

- 平衡所有计算机组件的速度与成本,实现整体性能最优

1.1.3 存储层次结构(Memory Hierarchy)

存储层次遵循局部性原理(Locality Principle),CPU 访问的数据具有时间局部性(近期会重复访问)和空间局部性(近期会访问相邻数据),因此将常用数据放在高速上层,不常用数据放在低速下层,兼顾速度与容量。

| 存储层级 | 访问时间 | 核心特点 | 典型介质 |

|---|---|---|---|

| Cache(高速缓存) | ≈5~50 ns | 速度极快、容量小、随机访问、双极型 SRAM、成本高;每个块附带元位(标记位 / 有效位)用于命中判断 | CPU 片内 / 片外 SRAM |

| Main Memory(主存) | ≈100~500 ns | 随机访问、成本适中、MOS 型 DRAM | 系统内存(DRAM) |

| Secondary Memory(二级存储) | ≥5000 ns(DASDS) | 直接访问 + 顺序访问、大容量、低成本 | 机械硬盘 / SSD |

| Auxiliary Memory(辅助存储) | 分钟级 | 离线归档存储、顺序 / 直接访问、极低单位成本 | 磁带、DVD-ROM、移动硬盘 |

注:DASDS = Direct-Access Storage Devices(直接访问存储设备),可直接寻址,区别于磁带这类顺序访问设备。

未完待续!