1 闩锁效应(Latch-up)

CMOS 电路的一个主要问题是器件闩锁效应,这是一种内部反馈机制,是在 CMOS 电路的电源引脚(VDD)与地(或 VSS)之间形成低阻抗通路的一种状态。该状态由触发因素(电流注入或过电压)引起。一旦被触发,即使触发因素消失,低阻抗通路仍可能持续存在,这种低阻抗通路会导致电路功能暂时或永久丧失。闩锁效应是基于体硅晶圆制造的 CMOS 电路所固有的问题。闩锁效应与电路密度密切相关,尤其是 NMOS 与 PMOS 的间距。随着 CMOS 特征尺寸持续缩小,横向与纵向尺寸按比例缩减,使得寄生双极型晶体管性能增强。

这里可以举个例子进行解释:把芯片想象成供水系统,那么芯片的电源就是家里的自来水总闸,芯片的地线就是地漏。在正常情况下,总闸的水只会顺着家里的水管流到各个水龙头,不会乱流。现在由于水管和地漏的安装结构,墙里藏了两个互相联动的泄洪阀(阀 A 和阀 B):如果正常用水,两个阀门都关死,不影响家庭用水,但如果出现意外的水压波动,比如楼下开水泵或有人猛开猛关水龙头,哪怕只是把阀A冲开一条小细缝,漏一点点水,这一点点水刚好冲开阀B。等到阀B一打开,漏出来的水就会反过来把A冲的更开,水流就会更猛,然后阀B就越大,这样循环就会陷入越开越猛,根本停不下来情况。在某个瞬间,两个阀门完全敞开,总闸的自来水就会通过两个阀门,一股脑涌进地漏里,形成一条几乎没有任何阻挡的大水沟。这样的结果就是:超大的水流撑爆水管,使得整个供水系统瘫痪,而且除非是把总闸关断,不然水流就永远不会停。

1.1 闩锁效应的开关工作原理

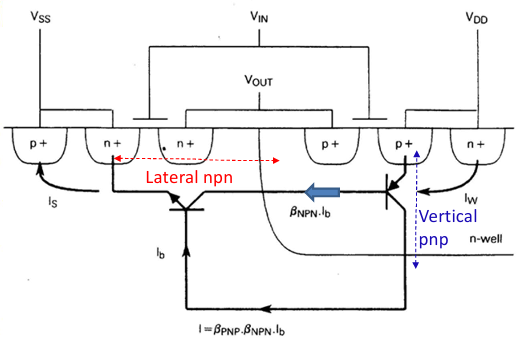

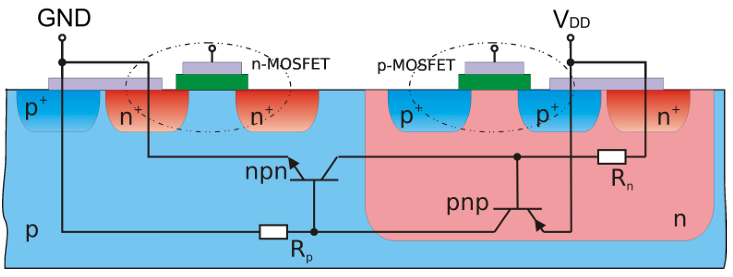

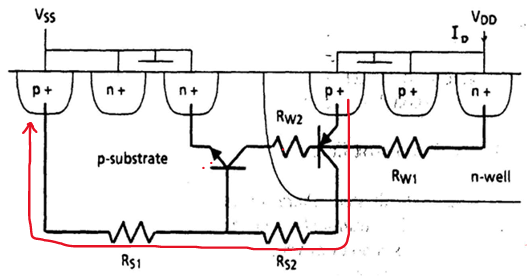

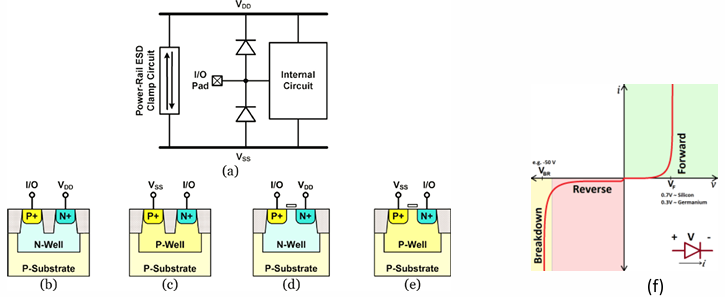

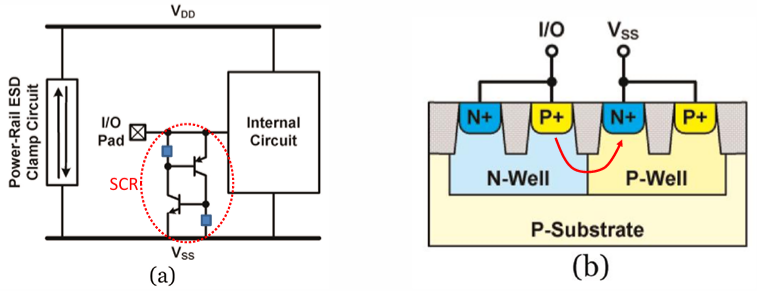

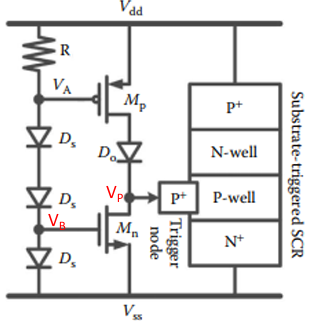

以 N阱-CMOS结构为例:在垂直方向上p+区、N阱和p型衬底构成了寄生纵向的PNP双极型晶体管;在水平方向上,n+区、p型衬底区和 N阱形成了寄生横向NPN器件,如下图所示:

寄生NPN管的发射极是接

此时两个晶体管都导通后,由于PNP管的基极与NPN管的集电极连接,所以NPN集电极电流

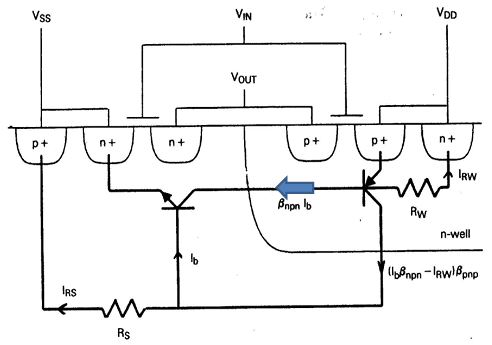

而要完整分析闩锁效应,我们还需要考虑如何考虑阱区与衬底电阻的影响。

接下来根据剖面图和电路图进行分析,考试以及面试必考,图一定要会画,并且会描述。

NPN集电极的电流

触发闩锁效应就需要让两个管子形成正反馈,进入NPN基极的电流必须大于原本NPN的基极电流,因此:

当加入衬底电阻和 n-well电阻建立模型时,对于NPN管,三个极的电流满足:

集电极电流为

此时 NPN管的发射极直接接

所以最终流到地的电流就是NPN发射极电流和衬底漏电流的总和:

将等式(2)代入不等式(1) 中可得:

最终这个不等式就是触发闩锁效应的必要充分条件。其中,

所以根据上面的不等式(3),我们可以发现,如果要避免闩锁,可以有两种方式:

- 降低NPN管和PNP管的共基极增益;

- 增加打开NPN管和PNP管所需的

1.2 闩锁效应产生的原因

一样是面试必问:

- I/O端口的信号变换超过

- ESD静电加压,从保护电路中引入带点载流子进入n-well或衬底中,也会导致SCR的触发;

- 许多驱动器一同工作,负载过大使得

另外,闩锁效应主要分为两类:

- 内部闩锁(ILU):由内部电路引起,如电源弹跳、片上传输线反射或载流子生成,触发体硅 CMOS 中的寄生 SCR。

- 外部闩锁(ELU):由 I/O 电路接收的片外信号触发,这些信号产生大幅电压波动或载流子注入。若载流子未限制在 I/O 单元内,可能触发 I/O 电路或邻近内部电路中的闩锁。

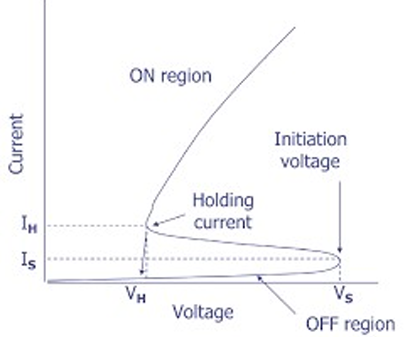

1.3 闩锁特性

1.3.1 雪崩击穿触发闩锁

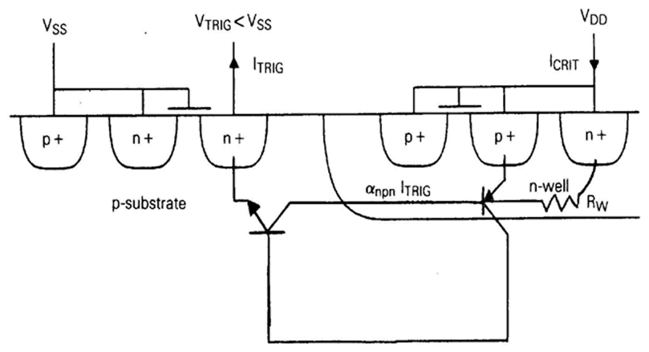

CMOS 的 N 阱(接

这个大电流流过

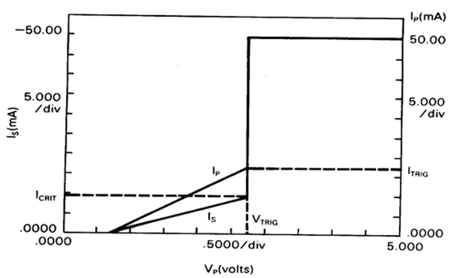

这里最重要的就是它的

曲线分为 3 个区域:

- 截止区(OFF region):电压低于触发电压,电流几乎为 0;

- 触发点(

- 导通区(ON region):器件闩锁导通,大电流低阻抗。

核心参数:

- 保持电流

- 保持电压

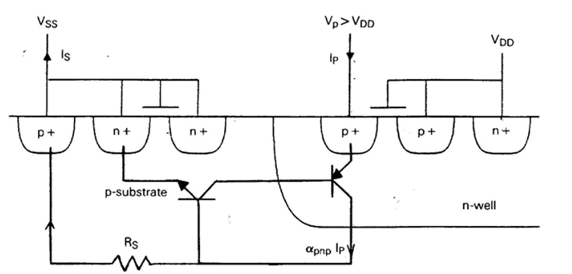

1.3.2 p+过压触发闩锁

p+过压就是PMOS管的p+源漏极电压被抬得比电源

下面给出

接下来是几个必考的核心参数以及公式:

随着p+区的电压(

- 触发电流

- 临界电流

- 触发电压

为了运算以及记忆方便,我们将触发电流和临界电流分别写为

上式中的

给出上述公式推导:

衬底电阻 Rs 上的压降为:

1.3.3 n+过压触发闩锁

和p+过压完全对称:n+过压就是NMOS管的n+源漏极电压,被拉得比地

接下来还是几个核心参数和公式必须记忆的:

在闩锁即将被触发前注入n+节点的电流(

其中,

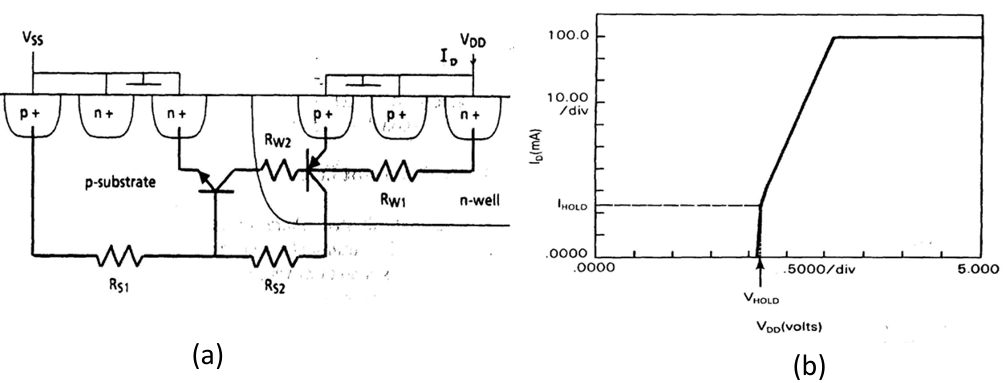

1.3.4 稳态闩锁保持特性

闩锁一旦被触发,就算撤掉触发信号,也不会自己关断,会一直保持导通状态,这就是闩锁的保持特性。只有把电源电压或电流降到足够低,才会回到关断状态。

-

保持电流

-

保持电压

- 测量方法:

- 先通过过压把器件触发到闩锁态

- 撤掉触发信号,缓慢降低电源电压

- 当电源电流突然暴跌(器件回到高阻态),此时的电压就是

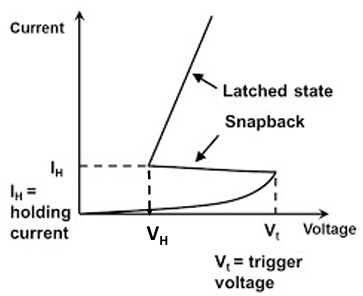

1.3.5 回滞测量(Snapback)与保持特性

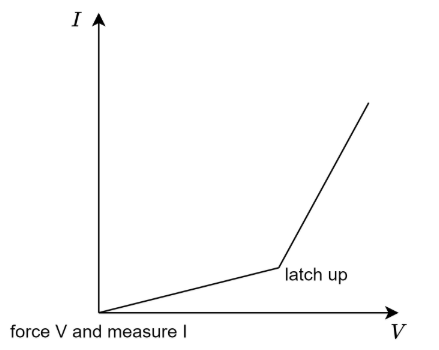

这是恒流测电压(force

当电压升高到触发电压

这里需要记住

当我们用恒压测电流(force

1.4 闩锁预防措施

1.4.1 基于闩锁的充分必要条件

根据我们前面推导出的不等式(3),我们预防闩锁效应的思路就是让闩锁发生的充要条件永远无法满足,主要采取以下两种实现路径:

- 降低环路增益:减小寄生双极晶体管电流增益;

- 提高触发电流阈值:通过降低阱电阻和衬底电阻来增加所需触发电流(

1.4.1.1 降低环路增益

要降低环路增益

基区越宽

电流穿过基区时被复合掉的越多 电流增益 越小。

CMOS 里有两个寄生 BJT:

- 横向 NPN 管:发射极是 NMOS 的 n+,集电极是 n 阱,基区是中间的 p 衬底,基区宽度就是n+ 和 p+(PMOS 的N阱里的 p+)之间的水平距离,也就是NMOS管和PMOS管的间距。

- 垂直 PNP 管:发射极是PMOS管的 p+,集电极是 p 衬底,基区是N阱,基区宽度是N阱的垂直厚度,几乎不受水平间距影响。

所以把NMOS管和PMOS管的间距拉大,n+ 和 p+ 的距离就变远了,横向NPN管的基区宽度就变宽了,

闩锁对 n+ 到 p+ 间距具有依赖性。对于 n+过电压应力,触发电流随着 n+ 到 p+ 分离的扩大而迅速增加。随着 n+ 到 p+ 间距的增加,

这里有一个很重要的问题:为什么增加 n+ 到 p+ 的间距会增加 n+ 过压触发的触发电流,而对 p+ 过压触发的触发电流影响不大?

Explanation:n + 过压触发的是横向NPN管,该NPN的基区宽度直接由n+到p+的间距决定,也就是说它的放大能力对间距高度敏感;而 p + 过压触发的是纵向PNP管,放大能力几乎不受间距影响。

1.4.1.2 提高触发电流阈值

要触发闩锁,必须让寄生三极管的发射结正向导通(需要 $ \simeq 0.7V$ 的电压),这个电压由电流流过衬底电阻

简单来说就是电阻越小,相同电流产生的电压就越小,很难凑够

有两种实现方式:

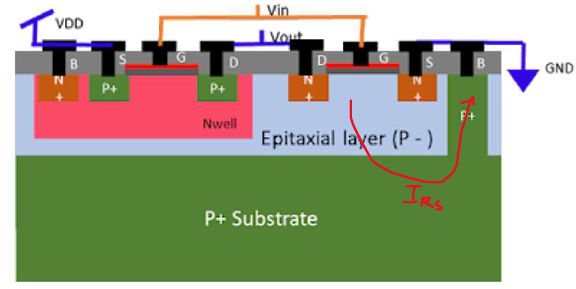

-

降低衬底电阻

在重掺杂的 p+ 衬底上,生长一层很薄的轻掺杂 p 型外延层,器件做在薄外延层上。

-

原理:

薄外延层让外延电阻很小,重掺杂的 p + 衬底本身电阻几乎为 0,因此总电阻RS大幅降低。

-

优势:重掺杂衬底远离器件的工作区,不会影响 MOS 管的正常性能。

-

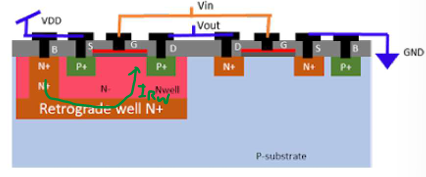

-

降低阱电阻RW:采用倒掺杂阱(retrograde well)

结构:和传统阱"表面掺杂高、底部掺杂低"相反,倒掺杂阱的阱底部掺杂浓度高,表面掺杂浓度低。

- 原理:阱底部高掺杂,直接把阱的体电阻

- 效果:对 n+ 过压触发的闩锁改善效果最显著,相比传统N阱,倒掺杂阱的闩锁触发电流大得多,抗闩锁能力更强。

- 原理:阱底部高掺杂,直接把阱的体电阻

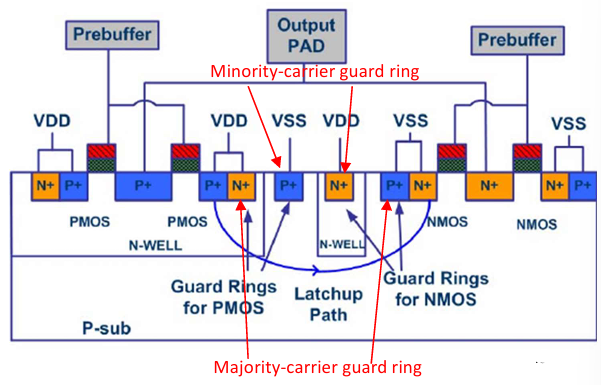

1.4.2 保护带(guard bands/guard rings)

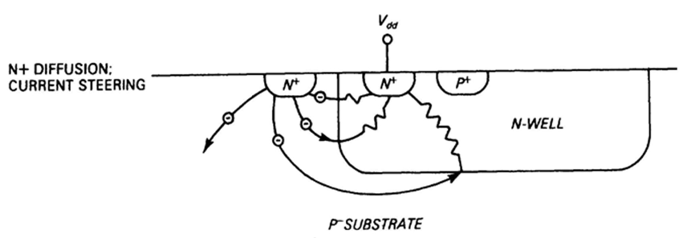

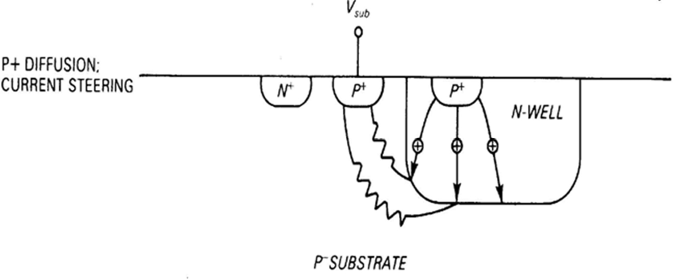

保护带就是在NMOS管和PMOS管之间、或器件周围,加接固定电位的掺杂扩散区,提前"拦截/导走"会触发闩锁的载流子,切断寄生三极管的触发路径,从根源阻止闩锁正反馈的建立,是 I/O 电路抗闩锁的核心手段。

其实就是把接阱或衬底电位的 n+、p+ 扩散区,放在NMOS管和PMOS管之间(或把器件围起来),这些扩散区就是保护带。

n+ 保护带(N阱内):接 VDD,把N阱里的电子电流 “转向” 导走,不让电流去触发纵向PNP寄生三极管;

p+ 保护带(p 衬底内):接 GND,把 p 衬底里的空穴电流导走,不让电流去触发横向NPN寄生三极管。

给保护环,把器件围起来,虽然抗闩锁效果更强,但会占用更多芯片面积。

保护环分为多子载流子保护环和少子载流子保护环两大类:

-

多子载流子保护环

就是上面的基础款保护环,核心作用是提前收集多子载流子,有效解耦寄生 BJT 的触发作用;是最常用的类型,内部电路受面积限制,通常只使用这种保护环。

-

少子载流子保护环

利用反偏的阱或衬底 PN 结,收集注入的少子载流子,彻底阻止载流子扩散触发闩锁。

在 p衬底的体 CMOS 工艺中,其N阱结深更深,因此N阱做的少子保护环,效果远好于普通 n+ 扩散的保护环;

p+ 少子保护环收集N阱里的少子(holes);n+ 少子保护环抑制 p 衬底里的少子(Electrons)注入。

在 I/O电路中,一般推荐同时使用多子和少子保护环

而因为受芯片面积限制,所以内部电路极少用多子和少子的组合,通常只单用多子载流子保护环。

另外,给P阱或N阱周围的保护环做密集的接触孔(frequent contacts),可以降低了寄生电阻(parasitic resistances)。

1.4.3 深层氧化物沟槽隔离(Deep oxide trench isolation)

第三种闩锁预防的方式是用物理绝缘的深沟槽,彻底切断寄生三极管的耦合路径,从物理层面杜绝闩锁的发生与持续。

在NMOS管和PMOS管之间刻蚀深沟槽,填充绝缘的氧化物(二氧化硅),相当于在寄生NPN、PNP三极管之间插入一堵"绝缘墙":

-

直接切断两个三极管之间的载流子传输路径,让它们无法形成闩锁所需的正反馈回路(即解耦);

-

同时大幅降低两个寄生三极管的电流增益,让环路增益远小于 1,彻底破坏闩锁的触发条件。

-

可以提升闩锁维持电压(Holding Voltage)

维持电压定义:闩锁一旦触发,要维持住电源-地短路的闩锁状态,所需的最低电压。维持电压越高,闩锁越难持续保持。

沟槽越深,闩锁维持电压越高。

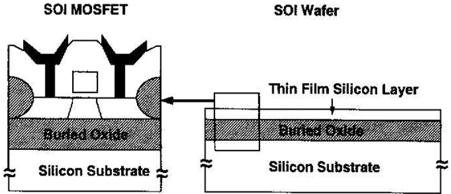

1.4.4 绝缘衬底硅晶圆(SOI(silicon on insulator) wafer)

SOI 完全避免了闩锁,因为它们没有寄生NPN和PNP晶体管。

1.4.5 大闩锁保护窗口(Large Latch-up Protection Window)

闩锁保护窗口就是电源电压

因此我们的目标就是扩大保护窗口,其本质就是提高

1.4.5.1 提高

这里的

其中,

我们可以用表格更直观:

| 调整对象 | 操作方式 | 原理 | 对应工艺 / 版图技巧 |

|---|---|---|---|

| $R_ { s_2 } $(n+到n 阱电阻) | 增大 n+到 p+ 间距 | 间距越大,$R_ { s_2 }

|

增加 NMOS/PMOS 横向间距 |

|

|

采用 p+衬底和薄外延层 | 薄外延层降低

|

外延衬底工艺 |

|

|

采用倒掺杂阱(Retrograde well) | 阱底部高掺杂降低

|

倒掺杂阱工艺 |

1.4.5.2 降低

因为闩锁的发生和维持需要两个关键条件,一个是寄生 BJT 的

而降低 VDD 可以同时破坏这两个条件:

- 当

- 当

在5nm等先进低功耗工艺,核心电路

解释为什么如果保持电压大于电源电压,则无法维持闩锁。建议一种提高保持电压的有效方法。

当保持电压大于电源电压的时候,即使触发闩锁,电源电压也无法维持

和 ,导致寄生晶体管截止,闩锁无法持续。 而要想提高电压,可以通过使用重掺杂 p+ 衬底和使用薄外延层能减小

;通过增加 n+到N阱之间的距离能增加 。其中最有效的方法是在 p + 衬底上使用外延层。

1.4.6 Multiple tap cells

tap cell是专门用于提供阱/衬底接电位的标准单元,替代传统单元自带的接电连接,核心目的是节省芯片面积。

我们用表格总结一下传统的标准单元、Tapless cell以及Tap cell,方便直观看出区别:

| 类型 | 结构特点 | 面积消耗 | 应用场景 |

|---|---|---|---|

| 传统标准单元 | 每个单元内部自带 n-well 接

|

面积大 | 早期 CMOS 工艺 |

| Tapless cell | 单元内部无阱/衬底接电连接 | 面积小 | 现代主流设计 |

| Tap cell | 独立的专用接电单元,为周围多个Tapless cell统一提供**n-well

|

面积节省显著 | 现代标准单元库 |

Tap cell有两个很重要的作用:

-

预防闩锁(Latch-up Prevention)

Tap cell提供低阻电流路径(low resistance paths for current flowing):n-well 接

-

避免浮体效应(Floating-body effect)

若阱/衬底悬空(floating),电位会随噪声漂移,影响器件性能;

Tap cell有几个关键的设计规则:

- 间隔布置:Tap cell按固定间隔插入,无需每个单元都接电,最大化节省硅面积;

- 多点布置:大尺寸器件/高噪声场景需放置多个Tap cell(multiple numbers of tap cells are placed around the devices),确保吸收噪声、维持恒定体电位;

- 纯物理单元(physical-only cell):Tap cell无输入/输出,仅负责接电,不参与逻辑功能。

1.4.7 Bulk FinFET 工艺下的闩锁预防

这一块内容了解即可,不做要求。

FinFET里,闩锁效应依然存在。因为FinFET虽然用了 3D 沟道结构,但源漏区还是和平面CMOS一样,做在N阱/p衬底里,依然会形成寄生的晶闸管结构 —— 闩锁的物理根源没消失,风险依然存在。

和平面 CMOS 思路一致,核心目标是提高触发电流和维持电压,常用方法:

- 增加阱接触(well pickups,即 tap cell),降低阱电阻;

- 插入双保护环(double guard rings):n 阱里的 n + 保护环、p 衬底里的 p + 保护环;

- 其他平面工艺方法也适用,比如增加 n±p + 间距、使用外延衬底等。

2 集成电路中的ESD和EOS保护

在集成电路中产生高能量/短持续时间的电感应损伤主要有三种机制:

| 损伤类型 | 特点 |

|---|---|

| 静电放电(Electrostatic discharge, ESD) | 持续时间极短(<1μs),比如摸芯片时的静电火花,电压高但功率极低 |

| 电过应力(electrical overstress, EOS) | 持续时间更长(微秒到毫秒级),是更宽泛的"过压/过流事件" |

| 闩锁效应(Latch-up) | 不受控的电流导通,会造成类似 EOS 的损伤;反过来 EOS 也可能触发闩锁 |

在纳米级 CMOS 工艺下,器件尺寸缩小,这三种失效会越来越严重,因此 ESD/EOS 防护是芯片商业化的核心技术。

对 EOS 和 EDS 给出简单定义:

- 电过应力(Electrical Overstress, EOS):广义上被定义为"器件承受了超过额定最大值的电流或电压,无时间限制"。

- 静电放电(Electrostastic Discharge, ESD):不同静电电位的物体或表面之间的静电电荷转移(比如摩擦起电后的放电),是 EOS 的一种子集。

- 广义和狭义区分(IC 行业)

- 广义 EOS:包含 ESD 在内的所有过压或过流事件;

- 狭义 EOS:特指非静电引起的过压或过流事件,和 ESD 是并列概念。

| 特性 | ESD 事件 | 狭义 EOS 事件 |

|---|---|---|

| 成因 | 摩擦起电 / 静电场诱导 | 非静电或非摩擦起电诱导 |

| 电压 | 高压(kV 级) | 较低(刚超过额定最大值即可) |

| 持续时间 | 极短(

|

长(毫秒甚至持续) |

| 功率 | 极低功率 | 低功率 |

关于 ESD ,有三种标准的模型

- HBM(人体模型):人体带静电后接触芯片放电(最常见场景);

- MM(机器模型):设备或机器带静电后接触芯片放电;

- CDM(充电器件模型):芯片自身带静电,接触导体后放电。

| 模型 | 全称 | 放电路径 |

|---|---|---|

| HBM | 人体模型 | 人体带电后通过肢体

|

| MM | 机器模型 | 自动化设备或工具带电

|

| CDM | 充电器件模型 | 芯片自身带电

|

2.1 ESD模型

2.1.1 人体模型(HBM)

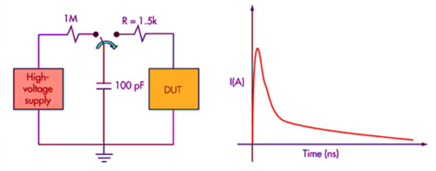

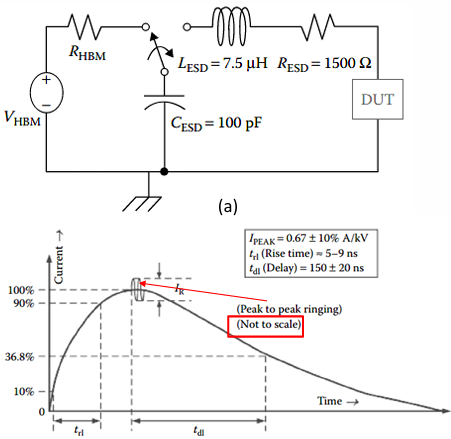

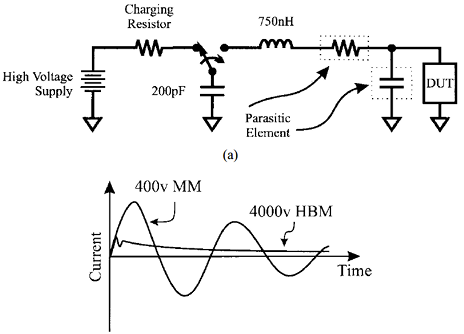

模拟人体接触芯片引脚时,向低电位或地放电产生的瞬态电流应力。将其模型化为电路,使用100pF 电容(模拟人体电容)和1500Ω 电阻(模拟人体电阻)。电容先充电到高压,再通过电阻向被测器件(DUT)放电,形成瞬态电流。理想的电路图和电流波形如下所示:

但在真实世界里,人体参数不是固定值:

- 寄生电感:5~10nH(测试仪器也会引入额外电感)

- 人体电容:167~514pF(和鞋子材质有关,比如绝缘鞋电容更大)

- 皮肤电阻:1kΩ~100kΩ(和皮肤油脂、出汗量有关,越干电阻越大)

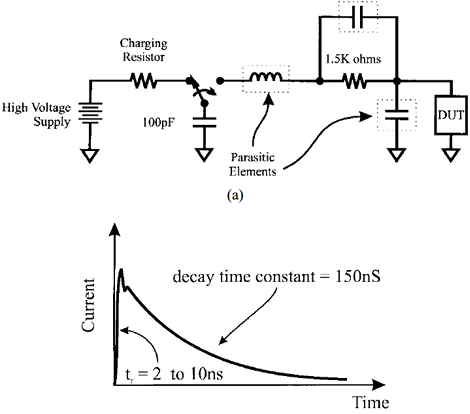

若同时考虑人体的电阻、电容与电感(

记住非理想的 RLC 电路图和波形就可以了,一定要会画图!

最终我们将其视为 DUT 阻抗为 0 的理想 RLC 电流源来进行建模,这也是IEC标准的理想 RLC模型,相比上面非理想的 RLC 电路,去掉了额外的寄生电容,是简化后的模型:

2.1.2 机器模型(MM)

MM主要发生场景是模拟工厂自动化生产中,带电的金属设备或工具(比如机械手、夹具、烙铁等)接触芯片导致的 ESD 损伤。一般是因为设备本身带静电(比如摩擦起电),接触芯片时会发生电弧放电,电荷直接冲进芯片。相当于"没有人体电阻限流的极端 HBM",人体摸芯片还有 1.5kΩ 电阻限流,而金属设备几乎没电阻,放电会猛得多。

电路图和波形图一定要会画!

-

标准电路参数:200pF 电容 + 750nH(0.75μH)电感,还有寄生元件(电阻、电容)。

电感直接控制电流的上升时间:电感越小,电流上升越快、峰值越高,对芯片的冲击越猛,是决定 MM 危害程度的核心因素。

从上图可以看到波形是欠阻尼振荡波形(因为电阻极小,RLC 电路阻尼很低,电流会来回震荡)。但在同样电压下,MM 的电流峰值远大于 HBM(比如 400V MM 的电流和 4000V HBM 差不多)。

2.1.3 充电器件模型(CDM)

CDM其实就是模拟芯片自己先带电,然后接触到地或低电位导体(比如金属桌面、测试机台)时,从芯片内部向外放电的 ESD 事件。通俗来说就是,HBM和MM是"外部打芯片",CDM 是"芯片自己炸"—— 芯片自身像个带电的气球,一碰地就瞬间放电。

- 原理:摩擦起电

- 典型例子

- 芯片在塑料包装管里滑动(芯片引脚 = 导体,塑料 = 绝缘体)。

- 芯片在测试机台(接地不良)的传送带上滑动。

- 结果:芯片整体带上正或负高压,此时接触地就会瞬间放电。

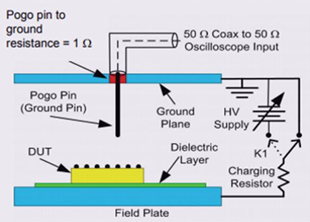

对CDM进行测试的方法如下:

- 芯片放在绝缘夹具(insulating fixture)上(引脚悬空)。

- 高压发生器(high-voltage generator)给芯片充电(125V~1000V)。

- 用探针(Pogo Probe) 接触芯片引脚,将芯片接地,瞬间放电。

接下来CDM模型的放电波形一定要会画,必考:

2.2 ESD预防措施

从器件上来划分,主要有下面两种预防措施:

(1) 处理 ESD 敏感器件

主要有以下几点内容,了解即可:

-

工作区(Work area)——必须在防静电工作站操作

要求处理 ESD 敏感器件(SSD),必须在防静电工作站(Static-safe workstation)进行。如果无法使用防静电手腕带,或者工作站上有无法移除的绝缘材料时:

- 使用离子风机(Air ionizer):它能吹出带正负电荷的离子,中和物体表面的静电。

- 涂抹局部抗静电剂(Topical anti-stats):抑制静电的产生和积累。

-

人员操作(Personnel)—— 先放电,再动手

工作人员在打开装有芯片的保护容器前,必须先释放身上积累的静电。

操作方法

- 先用手摸一下接地表面(Ground surface),把电导走。

- 最理想的操作应该是佩戴防静电手腕带(Wrist-strap),直接通过人体保护电阻接地,彻底泄放电荷。

-

包装与运输(Packaging and Transportation)—— 全程罩住

芯片在存储或运输过程中,必须时刻放在防静电包装袋(Static protective bag)或容器中。防静电袋(如屏蔽袋)是导体,能把芯片屏蔽起来,使芯片内外电位相等,避免芯片在运输摩擦中带电或被静电击穿。

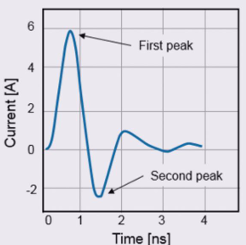

(2) 片上 ESD 保护(On-chip Protection)

为了保护芯片内部的精密电路(Internal circuits)不被破坏,需要在在芯片的引脚(Pad)周围设计"保镖"电路(ESD Clamp)。这样做的作用就是:

- 钳位电压:当高压 ESD 来袭时,迅速把电压钳制在安全范围内,不让高电压冲进内部电路。

- 泄放电流:提供一条低阻抗通路,让几安培的大 ESD 电流直接流向地,避开内部电路。

而芯片里的 ESD 保护电路主要分两类,列出表格较为直观:

| 类型 | 全称 | 通俗叫法 | 保护对象 | 核心作用 |

|---|---|---|---|---|

| Local clamp | 局部钳位 | 二极管 / IO 钳位 | I/O引脚 | 挡在输入输出引脚门口,防止引脚带电冲进来 |

| Power-rail clamp | 电源轨钳位 | SCR(可控硅) | 电源和地 | 守在电源(

|

ESD 有四种应力模式,也就是 ESD 放电的四个具体方向,对应 Local Clamp 的保护范围:

- PS 模式 (Positive-to-

- NS 模式 (Negative-to-

- PD 模式 (Positive-to-

- ND 模式 (Negative-to-

4 种 ESD 应力模式的工作逻辑要会描述:

| 模式 | 场景 | 二极管动作 | 电流流向 |

|---|---|---|---|

| PS(正→地) | I/O 带正高压碰 Vss | 下二极管正向导通 | I/O → 下二极管 → Vss |

| NS(负→地) | I/O 带负高压碰 Vss | 上二极管正向导通 | Vdd → 上二极管 → I/O |

| PD(正→电源) | I/O 带正高压碰 Vdd | 上二极管正向导通 | I/O → 上二极管 → Vdd |

| ND(负→电源) | I/O 带负高压碰 Vdd | 下二极管正向导通 | Vss → 下二极管 → I/O |

ESD 钳位电路(Clamp)必须满足 “一高一低” 的矛盾要求:

- 正常工作时(Normal):必须是断开状态(Off-state),漏电流(Leakage current)要尽可能小,不然会耗电、干扰芯片正常功能。

- ESD发生时(ESD Event):必须瞬间变成 低阻抗(Low-impedance) 通路,像开关一样 “啪” 地导通,把电流泄走。

电源轨钳位电路为 ESD 电流提供完整泄放通路,确保所有应力模式下都能有效防护。

片上ESD保护的总体目标,这个必背:

1. 核心防护功能

- 钳位 ESD 电压(Clamp the ESD voltage),分流 ESD 应力电流(hunt the ESD stress current)

- 提供 HBM、CDM 防护(protection for HBM and CDM)

2. 放电性能要求

- 快速导通(Turn on fast),响应 < 300ps(<300 ps response)

- 承载 1-2A的大电流(Carry large currents of 1–2 A or more),持续 150ns(for 150 ns)

- 导通电阻低(low on-resistance)

3. 芯片兼容性要求

- 焊盘(bond pad)占用面积最小(Occupy minimum area)

- 寄生电容最小(minimum capacitance)

- 串联电阻最小(minimum series resistance)

- 不增加静态漏电流(Not cause increased

- 不干扰芯片功能测试(Not interfere with the IC’s functional testing)

- 不引发闩锁(latch-up)或电过应力(EOS)失效

4. 可靠性要求

- 抗工艺漂移(immune to process drifts)

- 抗多次脉冲冲击(robust for numerous pulses)

- 耐受老化测试(Survive the burn-in tests)

记忆口诀:钳压分流(Clamp/shunt),快通低阻(Turn on/low R),扛流 150(1-2A/150ns);小面积(minimum area)、低容阻(minimum C/R),零漏测(no leakage/no test interference)、无闩锁(no latch-up/EOS);抗漂移(immune to process drifts)、耐脉冲(robust for pulses)、过老化(survive burn-in),双模防护(HBM/CDM)全搞定。

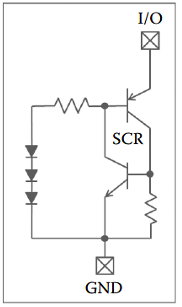

在 ESD 保护方案中有三种半导体器件常用于实现:二极管、栅极接地NMOS管(GGNMOS)和可控硅(SCR)。

二极管属于非回滞型器件(单向 ESD 保护器件),而 SCR 和 GGNMOS 属于回滞型器件(双向 ESD 保护器件)。这些器件均能在正负双向被触发并导通电。

但这三种器件各有缺点:二极管存在高漏电流问题,GGNMOS 健壮性较低,而 SCR 容易发生闩锁效应。

2.2.1 局部钳位(Local clamp)

2.2.1.1 二极管ESD保护

二极管能防护ESD的原理就是,当 ESD 高压出现在 I/O 引脚时,利用二极管**单向放电性(unidirectional discharging path)**进行正向导通(forward-biased),把大电流泄放到电源(

下面的图一定要记牢,必考:

| 结构类型 | 原理 | 特点 | 适用场景 |

|---|---|---|---|

| STI 限定二极管(STI-bounded) | 用浅沟槽隔离(STI,芯片的绝缘沟槽)隔离 P+或N+ 区 | 隔离效果好、漏电流小,但导通电阻大、ESD 鲁棒性弱 | 常规 ESD 防护、对漏电流要求高的场景 |

| 栅限定二极管(Gate-bounded) | 用 MOS 管栅极作为隔离,限定 P+或N+ 区 | 导通电阻小、ESD 鲁棒性强(扛大电流),但漏电流稍大 | 对 ESD 抗扰要求高的场景 |

上面二极管的I-V 特性图一定要会画。

当芯片引脚处于高工作电压(higher operating voltage)时,就可以使用堆叠二极管结构(Stacked Diodes)。因为单个二极管导通电压 0.7V,若芯片工作电压高(如3.3V或5V),单管会在正常工作时就导通,因此可以把多个二极管串联(stacked configuration),总导通电压就是二极管数量

堆叠二极管结构的优点就在于可以灵活调整导通电压,适配高电压芯片;但是缺点也很明显,占用芯片面积大、引脚寄生电阻增加,影响高频信号完整性。

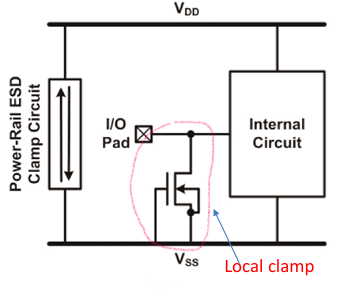

2.2.1.2 GGNMOS管ESD保护

GGNMOS,接地栅NMOS管(Grounded‑Gate NMOS),就是NMOS 管的栅极直接接地。GGNMOS实现ESD保护是局部钳位(Local clamp) 的一种,位于 I/O 引脚和地之间。在正常工作状态下,栅极接地,源极也接地,所以管子处于关断(off) 状态,完全不影响芯片正常功能。

工作机制必须掌握!

(1) 正 ESD 事件(Positive ESD)

当I/O引脚突然变成正的高电压(即PS/PD 模式)。

主要的保护流程如下:

- 触发(Avalanche Breakdown):I/O 脚(Drain)的正高压导致寄生 NPN 三极管的集电极-基极结发生雪崩击穿。

- 产生衬底电流:击穿过程产生大量衬底电流(

- 形成电压差:

- 导通 BJT:当

- 低阻通路(Snapback):一旦 BJT 导通,I/O 脚与地之间变成低阻抗(low on-resistance),电流顺畅流走,I-V 曲线上出现回滞效应(Snapback)。

(2) 负 ESD 事件(Negative ESD)

当I/O 引脚电压低于

主要的保护流程如下:

- 二极管导通:此时利用 GGNMOS 结构中的寄生结二极管(N+/P-Well) 正向导通。

- 低阻通路:二极管导通后,I/O脚和

- 电流流向:电流从 P-Well(

导通条件:

时,N+和P-Well结二极管导通。

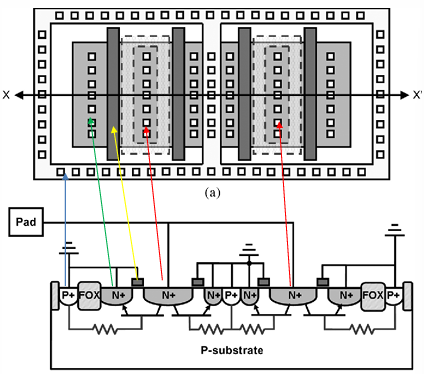

如下图所示,为了节省芯片面积,GNNOMS使用多finger结构(Multi-finger structure)。多指结构就是把多个单指结构(single-finger)并联,共享漏极(Drain)和源极(Source)区域。这样就可以在相同的面积下,增加总宽度,提升 ESD 鲁棒性。

上面共有4个GGNMOS。

我们想要GGNMOS的抗 ESD 能力强(robust),就得把结面积做大,但这又会导致寄生电容增加,也就是N+/P-Well 底部电容(Bottom capacitance)太大。为了解决这个问题,我们可以在 N+ 漏极下方注入额外的N阱(additional N-well),用N阱或P阱电容(sidewall capacitance)来替换掉大部分 N+/P-Well 底部电容,从而使得总电容大幅降低。

2.2.1.3 SCR用于ESD保护

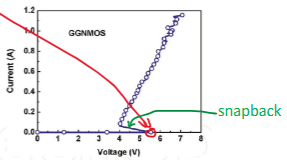

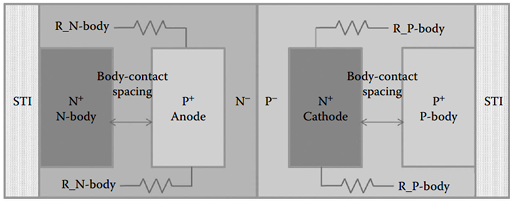

SCR,可控硅整流器(Silicon Controlled Rectifier),由一个横向 NPN 三极管和一个垂直 PNP 三极管组成的4 层(P+/N-well/P-well/N+)双向器件。

SCR有几个优势:

-

面积效率极高(Small layout area):在很小的版图面积下,就能提供极强的 ESD 防护能力。

-

低寄生电容(Low parasitic capacitance):这是高频电路(High-frequency circuits) 的福音,因为它对信号的干扰比二极管和 GGNMOS 都小。

-

无闩锁风险(Latch-up free):在低电源电压(low supply voltage) 的先进 CMOS 工艺中,SCR 可以安全使用,不会产生闩锁效应(这是之前 GGNMOS 需要担心的问题)。

-

双向防护(Bi-directional):既能防正 ESD,又能防负 ESD,无需像二极管那样堆叠或双向设计。

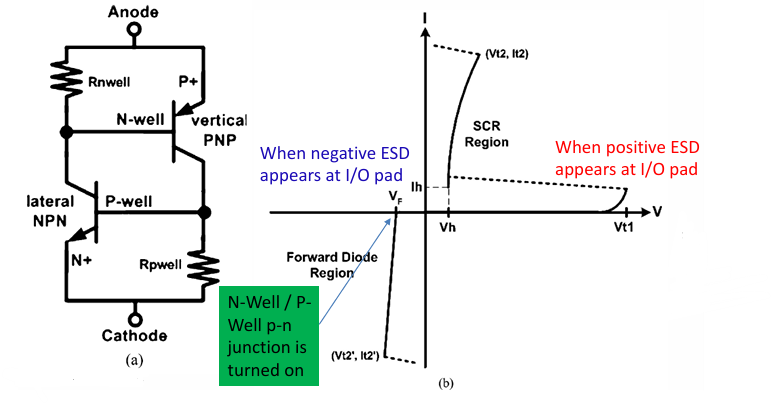

下面的电路等效图必须要记住,一定要会画图:

SCR 等效电路中有两个寄生电阻:

-

-

下面所示图给出了包含两个寄生电阻的SCR等效电路以及其直流 I-V特性图,一定要会画:

与GGNOMS一样,SCR也有两种工作模式:

(1) 正 ESD 事件(Positive ESD)

当I/O 引脚(阳极, Anode)突然出现正高压。

主要可以分成两个部分:雪崩击穿 + 正反馈锁存(Snapback)

-

雪崩击穿(Avalanche Breakdown)

- 当阳极电压超过N-well/P-well 结的雪崩击穿电压,发生击穿。

- 产生大量空穴(Hole)和电子(Electron)。

-

电压降触发 BJT

- 空穴电流流过 P 阱寄生电阻(

- 电子电流流过 N 阱寄生电阻(

- 空穴电流流过 P 阱寄生电阻(

-

正反馈锁存(Latching)

- 两个 BJT 一旦导通,就会形成正反馈(Positive-feedback regenerative mechanism):电流越大,电压越高,导通越彻底。

- 不需要再次雪崩击穿,就能保持导通状态(这就是 Latch 状态)。

最终,I/O 引脚与

(2) 负 ESD 事件(Negative ESD)

当I/O 引脚电压低于

-

二极管导通

- 此时利用 SCR 结构中固有的N-well/P-well 寄生结二极管正向导通。

- 导通电压约为

-

钳位作用

- 二极管把负电压钳制在

- 电流从 P-well(

- 二极管把负电压钳制在

记忆口诀

正压雪崩来触发,负压二极管顶一顶;

正反馈锁存低阻通,1.5V 保稳行。

2.2.2 电源轨钳位(Power-rail clamp)

如果说 I/O 引脚的保护(Local Clamp)是 “门卫”,那么电源轨(Power-rail)保护就是"大坝闸门"。其目的就是保护芯片内部的核心电路(Core Circuit),不让

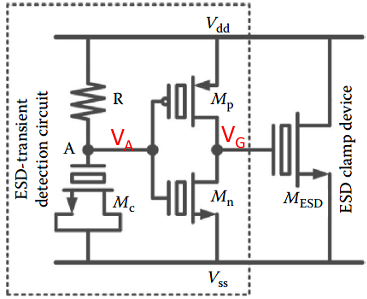

2.2.2.1 RC-based ESD检测联动大尺寸NMOS钳位

电路主要由两个部分组成:

-

RC 瞬态检测电路(RC-based ESD-transient detection circuit)

- 由电阻

- 作用:它是一个"延时器",用来识别 ESD 这种纳秒级的快脉冲,而不是芯片正常工作的微秒级信号。

- 由电阻

-

大尺寸 NMOS 管(Large-sized NMOS, MESD)

- 这是主开关管。

- 作用:ESD 来袭时,它导通,直接把

这里利用了ESD信号和RC电路的时间差(Time Delay)。因为ESD 信号的速度极快(上升时间$\sim

-

正常工作:

-

正ESD突袭(

-

- 虽然 A 点电压也想升,但RC电路反应慢,A 点电压上升慢得多(much more slowly)。

- 结果A 点电压还没来得及升高,而栅极电压

- 最终MESD 像闸门一样打开,

-

-

负ESD突袭(

-

- A 点电压因为耦合效应,可能导致

- 结果MESD不导通(注意:传统 RC 钳位主要防正ESD,负 ESD 可能需要辅助二极管或其他机制)。

-

但是在薄栅氧的先进工艺(GP 工艺)中,RC-based NMOS 因为漏电不可容忍且击穿电压不足,被淘汰了。SCR(Silicon-Controlled Rectifier))成为了电源轨钳位电路的主流器件(the main ESD clamp device),因为 SCR 没有栅极(no poly-gate structure),完全没有栅漏电流,且导通电阻极低,面积效率高。

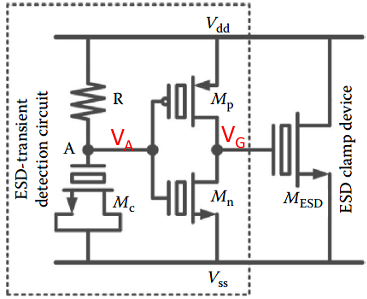

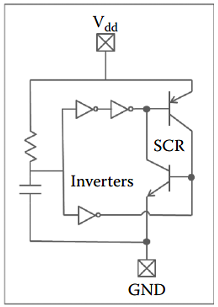

2.2.2.2 RC-based ESD检测联动SCR钳位

这个电路其实就是是上面RC检测和大尺寸NMOS方案的升级,专门解决先进 CMOS 工艺(薄栅氧、低电源电压)的几个问题:

- 大 NMOS 关断漏电流极大,静态功耗飙升;

- 薄栅氧导致栅氧漏电严重、击穿电压低,容易失效;

- 大尺寸 NMOS 占用大量版图面积,成本高。

它用可控硅整流器(SCR)替代大尺寸NMOS作为钳位器件,结合 RC 瞬态检测电路,既保留了 RC 电路识别 ESD 快脉冲的能力,又发挥了 SCR的"无栅氧、低漏电、高鲁棒性、小面积"的优势。

电路原理图一定要会画,而且要会描述工作流程!

电路也一样由两个部分组成:

-

电阻

和传统 RC 电路逻辑一致,也是利用时间差区分ESD 快脉冲和正常工作慢信号

有两种工作状态,一定要记住:

(1) 正常工作状态

- A 点电压(RC 电路输出)完全跟随

- NMOS 管

- B 点低电平无法触发 SCR,SCR彻底关断,没有任何触发电流,整个电路漏电流极低,不会产生额外功耗。

(2) ESD 触发状态

分两种 ESD 场景:

-

正 ESD 事件(

-

- 触发逻辑:

- 结果:

- 所以B 点高电压触发 SCR 导通,SCR 在

-

-

负 ESD 事件(

-

- 触发逻辑:

- 结果:B 点低电平导致 N-well/P-well 结发生雪崩击穿,产生的电流触发 SCR 导通;

- 最终 SCR 就会导通,泄放负 ESD 电流,钳位电压,保护内部电路。

-

2.2.2.3 Diode-string ESD Detection联动SCR钳位

Diode-string检测和SCR 钳位是另一种电源轨 ESD 防护方案。它弃用了 RC 的"时间延迟"逻辑,转而利用二极管的"高电平触发”""特性,直接通过电压差来识别 ESD。

电路图一定要背,死记硬背也得记住,考试必考!

- 左侧是二极管串检测电路(Diode-string + R)

- Diode-string:多个二极管串联,放在

- 电阻

- 二极管

- Diode-string:多个二极管串联,放在

- 右侧:P 型触发 SCR(核心泄放开关)

- 结构依然是 P+

- 触发端:位于 P-well,由 B 点电压(

- 结构依然是 P+

接下来我们需要知道这一方案的工作流程:

我把正常工作、正 ESD、负 ESD三个场景的逻辑完全理顺,保证你看懂。

-

正常工作状态(Normal Operation)

- 场景:芯片正常上电,

- 检测端:

- 电流:电阻 R 上无电流流过。

- 触发逻辑:

-

-

-

-

- 结果:电路待机,无漏电。

- 场景:芯片正常上电,

-

正 ESD 事件(

- 触发点:

- 过程:

- 二极管串导通。

- 电流流过电阻

- A 点电压被拉低,

-

- SCR 触发导通,在

- 触发点:

-

负 ESD 事件(

- 触发点:

- 过程:

- 同样,二极管串导通。

- 电流流过电阻

- A 点电压被拉低,

- B 点拉高,SCR 触发导通,钳位负电压。

- 触发点:

二极管串方案不仅能防正 ESD,也能防负 ESD,因为电压差超过阈值时它都会导通。

我的理解:

二极管串就像一个 “电压门槛”。正常电压太低,门不开;ESD 电压太高,门一开,电阻

就 "吃醋 了(产生压降),立马把开关 打开,进而启动 SCR。

这里还有个小细节:为什么要加二极管

我个人的理解是:

在大 NMOS 方案中,大管待机漏电很大。这里用了

2.2.3 采用 SOI CMOS的ESD片上保护

2.2.3.1 SOI 二极管

2.2.3.2 SOI SCR

由于 SOI 中独特的器件特性, 在体 CMOS 中实现的相同 SCR 设计无法直接迁移到 SOI 技术中。采用 SOI 技术构建的 SCR 器件具有以下独特特性:

- 在薄硅膜中形成的横向 PNPN 结构

- 不存在与衬底的寄生器件

- 用于交叉耦合 PNP 和 NPN 的横向体接触方案

- 外部触发电路与主 SCR 之间的隔离

体硅 SCR 的触发是雪崩击穿以及衬底电阻压降,触发电压由阱电阻和击穿电压共同决定,数值适中,适配芯片工作电压。但 SOI SCR没有衬底电阻,触发完全靠PN 结直接雪崩击穿,触发电压远高于先进 SOI 工艺的工作电压(比如 1V 核电压),会直接击穿内部电路,完全无法使用。

因此必须给 SOI SCR 加外部触发技术,把触发电压从十几伏的击穿电压降到适配工作电压的安全值,目前主要有两种方案:二极管触发 SCR(DTSCR)和RC触发 SCR(RCSCR)。

(1) 二极管触发 SCR(Diode-triggered SCR, DTSCR)

- 外部串联二极管串,接到 SCR PNP 管的基极。

- 正常工作:

- ESD 来袭:电压超过二极管串导通电压(二极管数量

DTSCR适用于低电容、低电压的I/O口ESD 保护(局部钳位),比如射频 LNA(低噪声放大器)的 I/O 口。因为二极管串的寄生电容极低,不会影响高频射频信号的完整性,完美适配 I/O口的低电容需求。

我个人认为其实DTSCR就是给 SCR 装了一个电压门槛:正常电压太低,门不开;ESD 电压够高,门一开就触发 SCR,专门给 I/O 口用,不影响信号。

(2) RC触发 SCR(RC-triggered SCR, RCSCR)

- 由RC 网络 + 反相器链组成双路控制电路:

- RC 网络:负责检测 ESD,ESD 来临时触发 SCR。

- 反相器链:分别给 PNP 的 N-well 基极、NPN 的 P-well 基极提供触发电流;正常工作时,把 N-well 拉到和阳极同电位、P-well 拉到地(和阴极同电位),SCR 无正向偏置,漏电流极小。

- 正常工作:RC 无延迟,反相器链关断 SCR,漏电流极低。

- ESD 来袭:RC 延迟,反相器链输出触发电流,SCR 导通泄放。

RCSCR适用于对漏电敏感的电源轨钳位(Power-rail Clamp),比如电池供电的移动芯片电源。因为RCSCR 的漏电流极低,不会浪费电池电量,完美适配电源的低漏电需求。

我个人认为RCSCR就是给 SCR 装了一个时间检测器:只有 ESD 这种快脉冲才触发,正常慢信号不触发,专门给电源用,不耗电。

2.2.3.3 用于高压 ICs 的ESD片上保护

2.2.3.4 分段发射极拓扑

2.2.3.5 适用于120V SOI工艺的ESD保护设计

2.3 ESD 测试

这里我认为其他都不重要,只要记住TPL测试就可以了,但以防万一还是都讲了。

2.3.1 HBM 测试

2.3.2 CDM 测试

2.3.3 MM 测试

2.3.4 传输线脉冲(Transmission Line Pulse, TLP)测试

之前学的 HBM、MM、CDM 这些经典的 ESD 模型,本质是“黑盒测试”:

- 只能给芯片加一个复杂、极短的高压脉冲,最后只看"过/不过(pass/fail)";

- 完全看不到保护器件内部的工作过程,不知道它是怎么导通、哪里失效、参数是多少;

- 脉冲波形复杂,电路响应难以测量,无法提取器件的 I-V 特性。

而 TLP 是一种“白盒测试”,专门用来打开 ESD 的黑盒:

- 它能产生标准、可控的方波脉冲,精准模拟 ESD 的瞬态特性;

- 可以直接测量器件在 ESD 应力下的瞬态电流、电压,提取完整的瞬态 I-V 曲线;

- 能直接读出器件的关键参数:导通电压、保持电压、二次击穿电流等,彻底搞懂保护器件的工作机理。

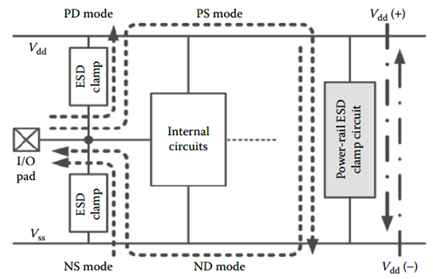

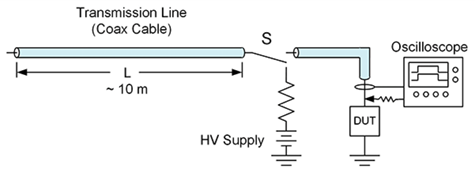

其主要组成有:一根约 10 米长的同轴传输线(Coax Cable),特性阻抗 50Ω;高压电源(HV Supply)给传输线充电到设定电压;开关 S会瞬间闭合,让传输线放电到被测器件(DUT);以及一个示波器(Oscilloscope),能实时测量 DUT 的电流、电压波形。

原理简单来说就是:TLP 就像一个 “精准的 ESD 模拟器”,用一根长电缆当"分布式电容",每次只给芯片打一个可控的方波,而不是 HBM 那种复杂的随机脉冲。

这一节最重要的就是瞬态电流和电压的时域测量方法,一定要记牢:

- 先给器件打一个低电压的 TLP 脉冲,测对应的电流,得到一个电压

- 慢慢提高脉冲的电压,每次测一个(

- 每次打完脉冲,给器件留 1~2 秒的散热时间,不会把器件烧坏;

- 把所有的点连起来,就是器件的瞬态 I-V 曲线,完美还原器件在 ESD 冲击下的完整行为。